|

DDR333 DQS |

2010/6/7 DDR266資料をアップデート |

DDRメモリは最近の高速メモリの代表になりつつあるものです。

ただ、設計は複雑な要件を満たさないとならず、なかなか手を出せないエンジニアも現在たくさんおられるようです。

複雑な要件のうち厄介なのがアナログ的ものです。HDLの設計が完璧であっても次元が異なる現実があります。

100MHzを超えますと必然的にアナログ要素が絡んできます。高速なだけにそのデバッグに高価なデジタルオシロの必要にせまられたりします。

100MHz以上の信号を測定するには、サンプリング

1G S/s は最低でも必要です。

当方のこの技術は、オシロ等価というテクノロジですが、2G

S/s あります。役に立つこともあると思います。

以下、1例です

(パーソナルなデジタルオシロでこの帯域幅を分析できるのは現在かなりレアです)

|

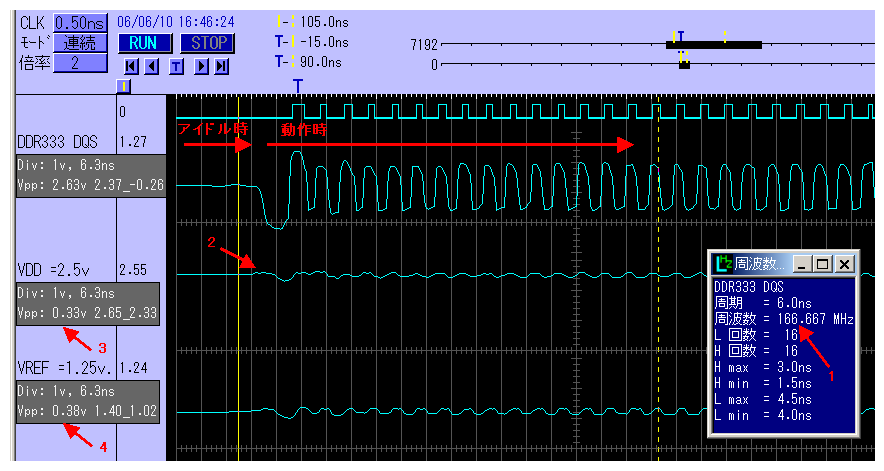

| 図1 |

●高電力使用からくる電源の調査

DDRでは、電源に対し低抵抗での終端をかなりの本数しなければならないため、電力負荷が大きいのが特徴です。

従って、動作時電力と、アイドル時電力に極端に違いが出ます。

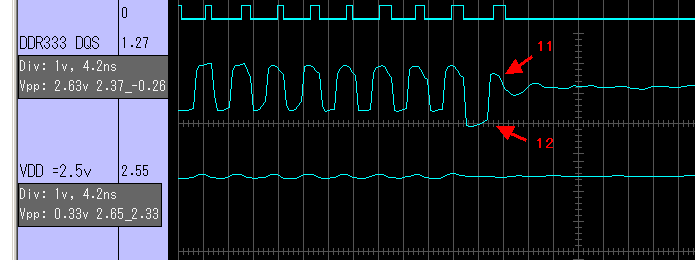

今回は、DQS(リード時)動作時に、電源にどれだけ負担がかかるかを見る目的で上図のような測定をしました。

信号DQSと電源VDD、VREFの同時測定です。

(この基板は、VDD=2.46V、VREF=1.22Vに設定されたものです)

矢印1、DDR333は、周波数では166MHzです。DQS開始時を動作時としています。矢印2、電源VDD、VREFは動作時からリプルが顕著になってきているのがわかります。

そのVppは、矢印3、VDD = 0.33V。矢印4、VREF = 0.38V。

(Vppの計測は、2本のカーソル間を対象に実行されます)

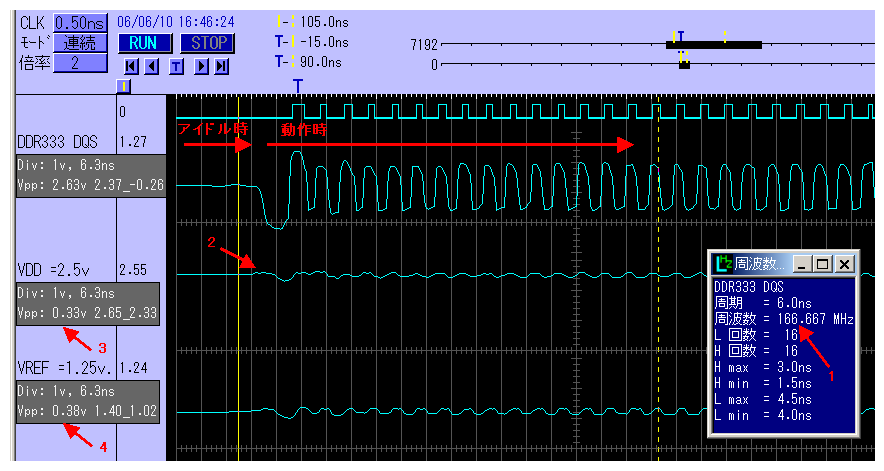

下図

倍率を下げて見ると、矢印5、動作終了と共に、リプルが戻っているのが見えます。

|

| 図2 |

この結果から、

電源の動作時リプルを減少させたければ、基板を調整して、また同じ測定...地道なデバッグが繰り返されて、安定動作の領域を求めることなります。

調整例

・電源レギュレータのLC値の見直し

・電源パスコンの見直し

・信号終端で過度な電圧負担がないかの見直し(終端抵抗値、抵抗数など)

...

※DDR電源はリプルを完全には除去できないはずです。どの程度に抑えるかという事だと理解しております。

このターゲットとなったDDR回路は、少なくとも、若干VREF

を安定させるべきでしょう。

補足

上図を注意深くみると、DDRの特質ともいえる現象が捕捉されています

矢印6、矢印7 の部分です。以下解説します。

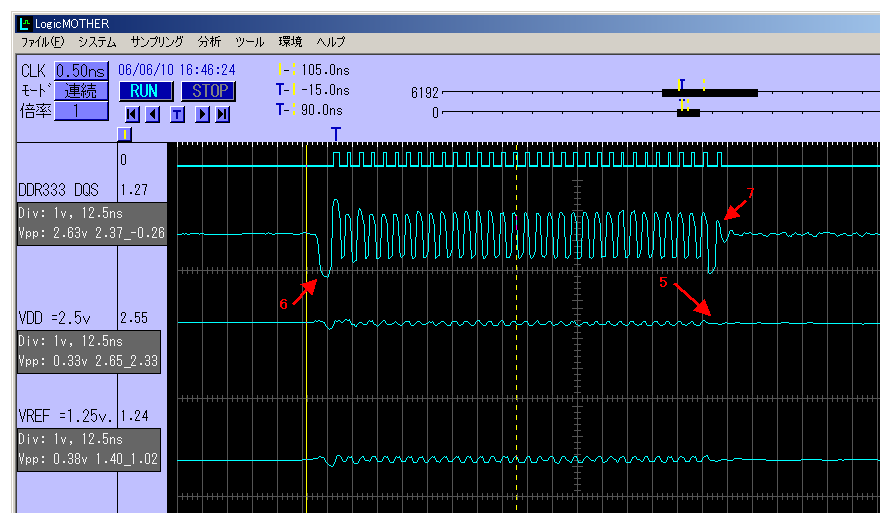

●起動時の特徴 矢印6

|

| 図3 |

このDQSはリード時なので、DDR側が発行しています。接続側は、ソースシンクとしてこれに同期をかけてデータ有効部の判定に使用します。

まず、矢印8 の開始時は、Hiz →1度L側に強ドライブ →

1発目のDQS 矢印9 となっています。これがもし、Hiz → 1発目のDQSだと、受け取り側は検出がうまくいかないと思います。さすが汎用メモリであるだけにしっかり作られているものです。アナログ波形で確認して納得できる現象です。

先に電源変動の話をしましたが、よく見ると、リプルの最大発生部は、矢印10 DQS1発目であり、動作中間ではそこほどではないこともわかります。

従ってポイントを絞る場合、DQS1発目になります。

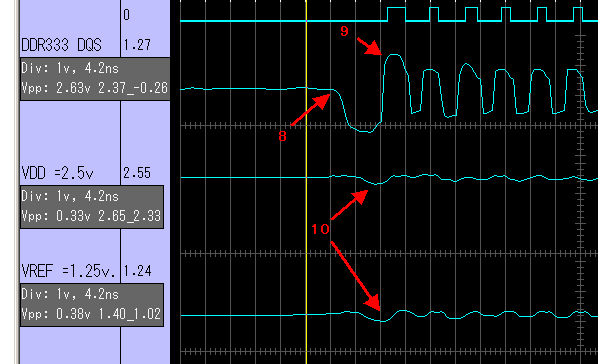

●終了時の特徴 矢印7

|

| 図4 |

矢印11の1個前がDQSの最後です。よく見ると、直前のL側が強ドライブされているのがわかります矢印12(微妙でわかりにくいですが)。設計上からもこのDQSは終了後であることは確認しています。

では矢印11は何。

DQSは非起動時Hizなので、ドライブが解かれるとき、VREF電圧値を中心に軽くリンギングをしながら落ち着きます。その程度は終端、電源強度に影響されます。それが検出されているわけです。正規信号より電圧が低いです。図2の矢印6、7を比べて下さい。DQSが起動する前は平坦で、終了後はリンギングが見れます。

接続側の回路は、DQS有効区間をイネーブルする設計をしていないと最後のデータだけ時々おかしくなるなど発生します。こういう現象を理解することが必要です。

当方も測定してみて非常に参考になりました。

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |