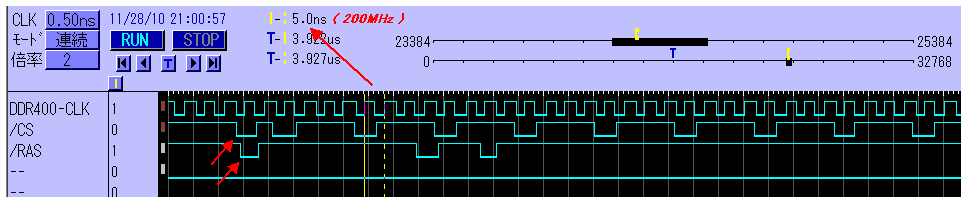

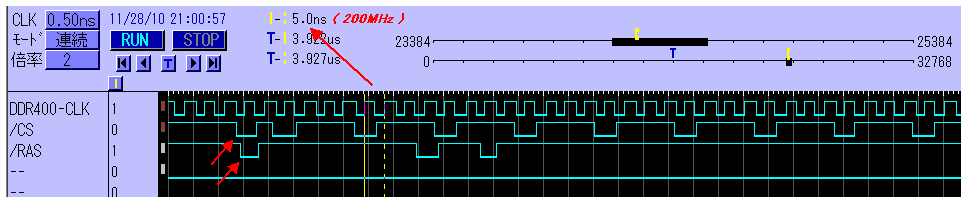

CLK(200MHz) - /CS, /RAS丂埵憡娭學

僒儞僾儕儞僌CLK丗丂 2G-4CH乮LHBUF4丂2屄儌乕僪乯

仠僴乕僪峔惉

崅懍僶僢僼傽LHBUF4傪2屄丄摨幉僾儘乕僽LBUF_PB 3杮丄掅斀幩IC僋儕僢僾LIC-S1巊梡

|

DDR2-400 |

丂CLK - /CS, /RAS |

CLK(200MHz) - /CS, /RAS丂埵憡娭學

僒儞僾儕儞僌CLK丗丂 2G-4CH乮LHBUF4丂2屄儌乕僪乯

仠僴乕僪峔惉

崅懍僶僢僼傽LHBUF4傪2屄丄摨幉僾儘乕僽LBUF_PB

3杮丄掅斀幩IC僋儕僢僾LIC-S1巊梡

|

仸摉儘僕僢僋傾僫儔僀僓乕偼丄僨儖僞僐傾幮僆儕僕僫儖奐敪偱偡丅

婰嵹偝傟偰偄傞奺柤徧丄惢昳柤偼丄奺幮偺彜昗丄傑偨偼丄搊榐彜昗偱偡丅 |