DDR2-400 のIO規格は、SSTL18です。

FPGAで作成する時、IOの種別を選択します。FPGAメーカーによって詳細種別があります。

あるメーカーでは、SSTL18-Ⅰ、SSTL18-Ⅱ があります。ドライブ能力が -Ⅱ の方が大きく、ファンアウトなどの用途で使い分けます。

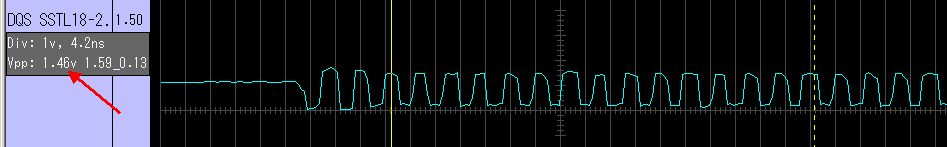

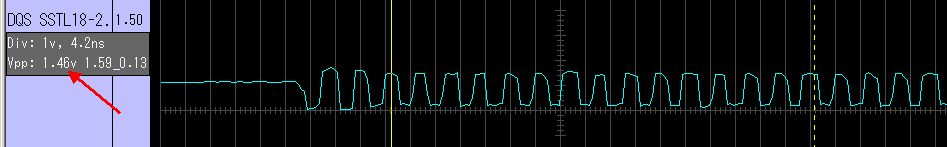

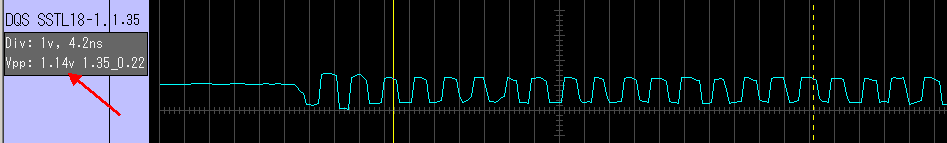

以下、DQS(WR側)で、違いを測定します

SSTL18-Ⅱ

|

DDR2-400 |

SSTL-IOの影響 |

DDR2-400 のIO規格は、SSTL18です。

FPGAで作成する時、IOの種別を選択します。FPGAメーカーによって詳細種別があります。

あるメーカーでは、SSTL18-Ⅰ、SSTL18-Ⅱ があります。ドライブ能力が -Ⅱ の方が大きく、ファンアウトなどの用途で使い分けます。

以下、DQS(WR側)で、違いを測定します

SSTL18-Ⅱ

SSTL18-Ⅰ

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |