電源ノイズの精密な測定

|

電源ノイズの精密な測定 |

|

|

| LDSO: デジタルストレージオシロの活用 |

||

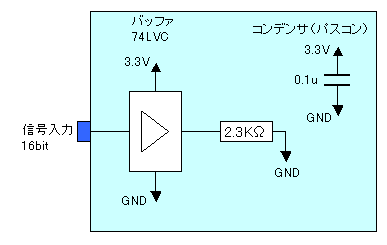

試験回路

|

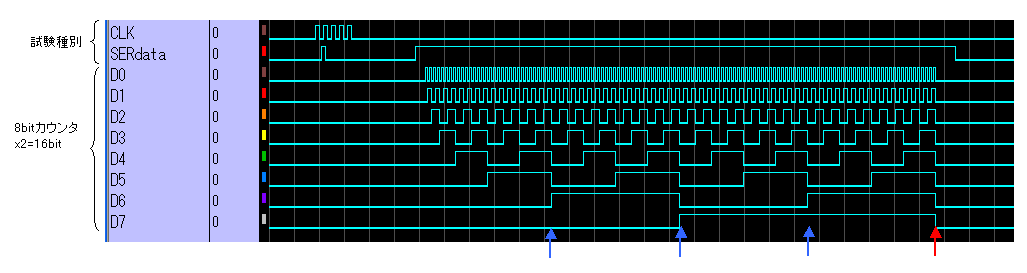

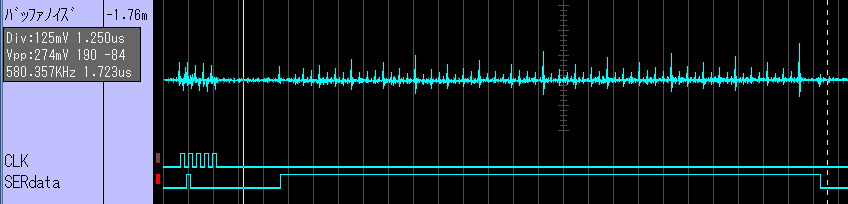

この回路は、バッファICのスイッチングノイズを測定するものです 信号入力に、データパタンを入力します。(信号発生機能を利用) バッファICはHL変化時にスイッチングノイズを発生するので、その電源ノイズを測定します |

|

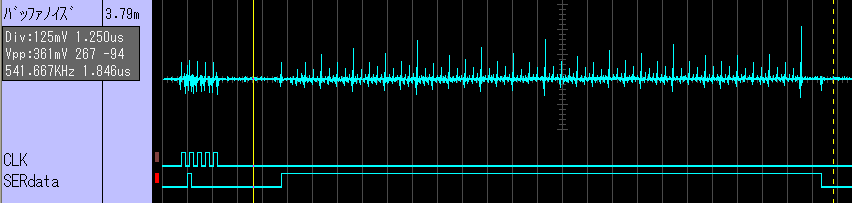

16bitカウンタ 動作中のノイズ (SERdata = 01000 B) Vpp = 361mV Div: 125mV, 1.25us |

|

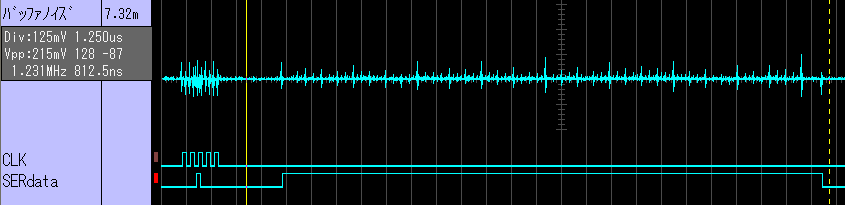

8bitカウンタ 動作中のノイズ (SERdata = 00100 B) Vpp = 215mV Div: 125mV, 1.25us |

|

|

| 一般的なオシロのノイズ測定法より優れたポイント |

| 微小ノイズを正しく測定する注意 |