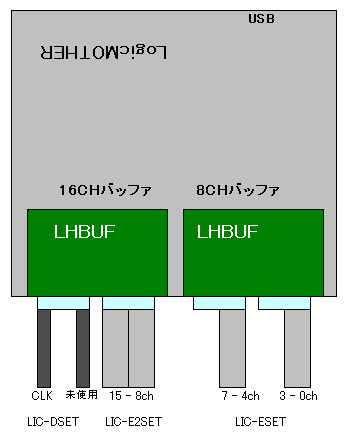

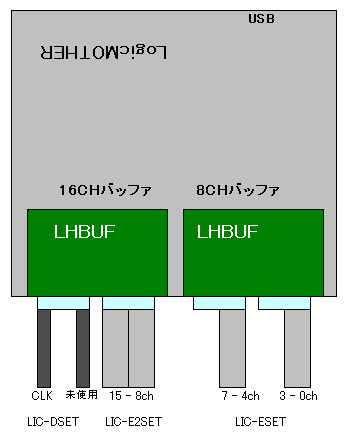

LIC-DSETは、CLK用で図のCLKをCLKに接続し、右は未使用

16CH時の必要構成

バッファ:2個

LIC-ESET:2個

LIC-E2SET:1個

LIC-DSET:1個

8CH時の必要構成

バッファ:2個

LIC-ESET:2個

LIC-DSET:1個

※FPGA内部+外部同時ロジアナで、低速使用なら、標準バッファ標準プローブを使うこともできます(上表参照)

|

外部CLK |

●旧来のロジアナの外部CLKの意味

旧来のロジアナの外部CLKは、メモリが数Kサンプルとかの少ない時代にメモリを無駄なく使用するため考案されたものです

当ロジアナは、多大メモリを持つので本来必要ありません、また、外部CLKを使用しなくてもエッジサンプリングできます

(外部CLKの問題点、エッジサンプリング機能。参照:検索&ステート )

●当ロジアナでの外部CLK対応の意味

サンプリングCLKを200MHzを超えると、1Mのメモリ制限があり、100MHzなどの高速分析にはメモリが1M以上使用できません

100M以上の高速同期サンプリングは外部CLKを使った方が良い場合もあります

そこで高速&ロングという特殊サンプリング用に外部CLKサンプリングが追加されました V5.8

●外部CLKの条件

※外部CLKは、RUN中、定速で停止しないことが使用条件です

| 外部CLK範囲 | 10MHz - 200MHz ※高速専用、ダブルデータレート不可 150Mbps/16CH(同時スイッチング対応)、 200Mbps/数CH(VCC=2V) |

| 分析CH数 | 16CH |

| 電圧 | 1.5 - 3.3V ※電圧によりバッファが異なる、LHBUF3、LHBUF・E |

| メモリ幅 | 標準1M、最大64Mサンプリング(オプション) |

※それ以下の低速CLK時は、サンプリングCLK200MHz以下でメモリ64Mサンプルが可能なので通常サンプリングをして下さい。検索&ステート 機能を利用下さい

●構成

外部CLKの高速フルセット

| バッファ | LHBUF3: 1.5 - 2.2 V LHBUF・E: 2.2 - 3.3 V |

どちらか2個 |

| ケーブル | LIC-ESET: 1個4CH LIC-E2SET: 1個8CH LIC-DSET: CLK用CH |

LIC-ESETは1個4CHを必要CH分、最低1個 LIC-E2SETは9CH以上時1個必要 |

FPGA内部+外部同時ロジアナで標準バッファを使う場合

| 150Mbps、外部15CH 200Mpbs、外部数CH |

外部CLKの高速フルセット |

| 100Mbps以下、外部数CH | LMBUF2を2個、標準プローブ+LIC-DSETを1個 LIC-DSETは、外部CLK-CHに使用 |

※基板の状態によってはそれ以下になります

※200Mbpsを使用する場合、外部信号数は数本以下にして下さい。例:CH0のみ200Mbps、CH3-7に低変化レートの信号

|

LHBUF*は、1個16CHですが、外部CLK時は1個8CH LIC-DSETは、CLK用で図のCLKをCLKに接続し、右は未使用 16CH時の必要構成 バッファ:2個 LIC-ESET:2個 LIC-E2SET:1個 LIC-DSET:1個 8CH時の必要構成 バッファ:2個 LIC-ESET:2個 LIC-DSET:1個 ※FPGA内部+外部同時ロジアナで、低速使用なら、標準バッファ標準プローブを使うこともできます(上表参照) |

●接続

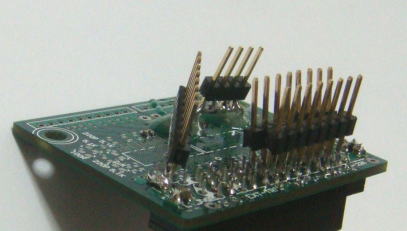

100MHz以上の高速計測は、非常に繊細にプロービングしなければなりません。この作業は結構時間もかかると思います。

特殊な形状のLIC-ESET、LIC-DSETを使用し、ICクリップは付けず、ヘッダピンに直挿入します

そのため、基板の信号とGNDに汎用ヘッダピンをハンダします

|

|

| 汎用ヘッダピン | ヘッダピンを信号にハンダしたところ |

|

GNDはこのように横にジャンパーをハンダし。両端を2箇所基板GNDにハンダするとやり易いです |

|

LIC-ESET を取り付けるとこうなります GNDは白ケーブルです。全て挿入しなければなりません 先端の可動部は25mmと小さいのでバスがまとまっていないと接続できません |

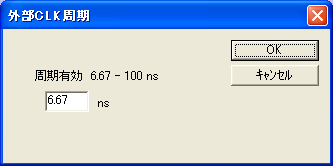

●CLK位相の設定

※初回のみ、まず機能を有効にする作業をして下さい。

メニュー → 環境 → 特別機能選択

CLKメニュー → ”EXT”

| UP delay | 立ち上がりからのデータ位相を選択、数字はns |

| DOWN delay | 立ち下がりからのデータ位相を選択、数字はns |

| 周期設定 | CLK周期を入力 (下記ダイヤログ) |

|

※6.67ns は150MHz 100nsは10MHz |

●操作

通常RUNと同じ

(16CHだとバッファは2個、8CHずつ使用しますが、アプリの表示CHは、連続の0-15

の位置になります)