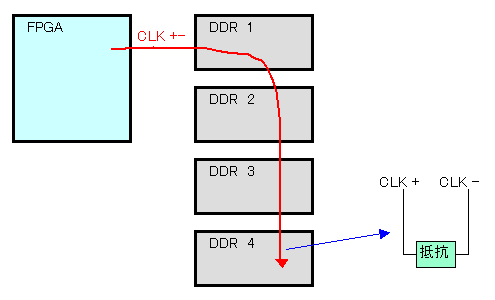

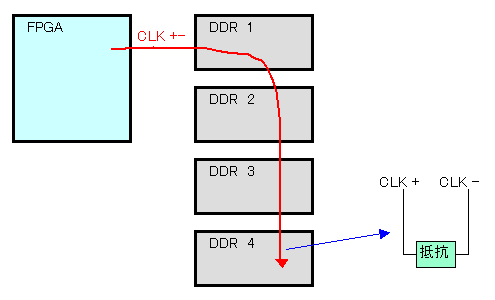

DDRが2個で、抵抗のみで終端する回路で実測して、抵抗がどう影響するかを検証します

SSTL18-2 (振幅規格1.8V) CLK=220MHz (DDR440相当)

|

DDRメモリのCLK品質評価 |

DDRが2個で、抵抗のみで終端する回路で実測して、抵抗がどう影響するかを検証します

SSTL18-2 (振幅規格1.8V) CLK=220MHz (DDR440相当)

|

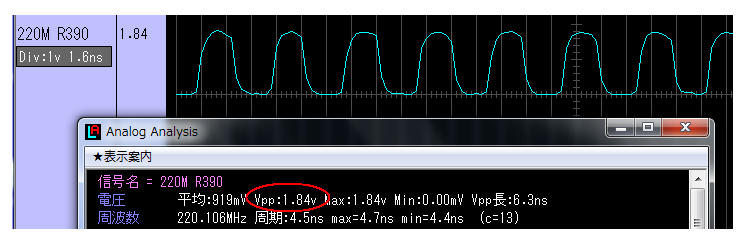

終端抵抗: 390Ω Vpp: 1.84V |

|

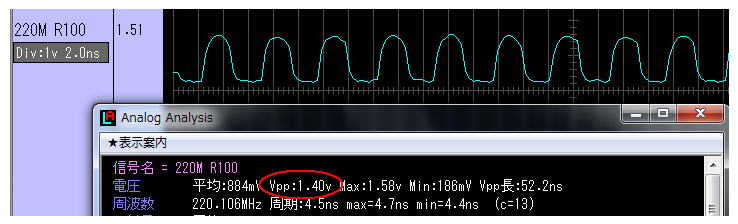

終端抵抗: 100Ω Vpp: 1.40V |

Vppは、1.5V程度は必要なので、この回路では終端抵抗は、100Ωでは適さないと判断できます

以上は、DDR個数、PCB状態、終端方式、...によって様々な結果になります

この検証は、HDL設計だけではわからないことです。しかし、回路動作安定解析には不可欠です