ツイスト線で、P/N差動で接続します。汎用ヘッダピン挿入用、別売ICクリップ装着可

8CH単位(5CH/LVDS、3CH/CMOS)

LIC-RLTCABLE

差動信号は接続困難な場合があるので、上のヘッダピンの無い直接ハンダするものも用意

|

差動 LVDSの測定用プローブ |

|

| パーソナルロジアナ業界初、差動プローブ LVDSロジアナ |

バッファ:LRBUFの派生機能として展開します

LVDSなど差動高速信号用

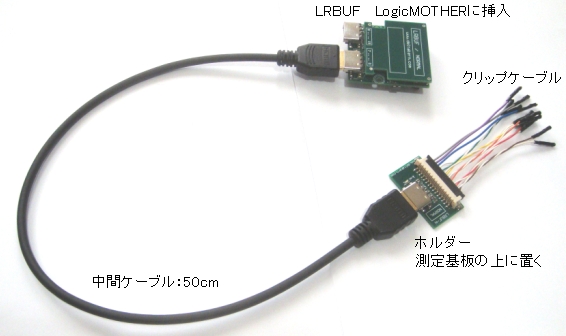

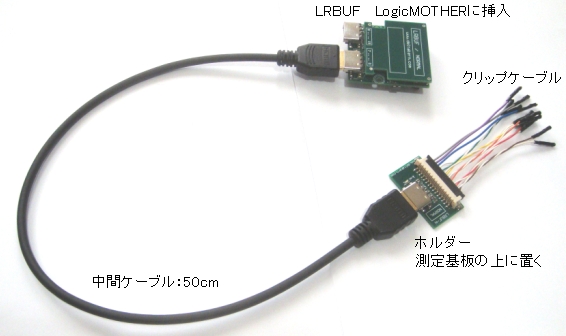

使用例

・LVDSシリアルデータを1フレームまるごとサンプリング

|

|

| ※ホルダー下面は絶縁されているので直に基板の上にに置けます | LIC-RLTSET ツイスト線で、P/N差動で接続します。汎用ヘッダピン挿入用、別売ICクリップ装着可 8CH単位(5CH/LVDS、3CH/CMOS) LIC-RLTCABLE 差動信号は接続困難な場合があるので、上のヘッダピンの無い直接ハンダするものも用意 |

●1バッファ 16CH 8CH単位x2

8CH単位解説

| 0-4 CH (5CH) | LVDS用 ツイスト線で、P/N差動で接続します |

| 5-7CH (3CH) | CMOS用 単線で接続します スレショルド固定。振幅範囲1.5-3.3V |

| ノーマル | 送受信が確立されたLVDSラインをリードする |

| 差動終端 | 送信だけのLVDSラインに対し、受信側としてリードする ※差動終端100ΩがLRBUF内部で有効になります |

| CH数 | 16CH 8CH単位x2 ※2バッファ = 32CH ※サンプリングCLK=0.66nsは通常バッファ同様半分のCH |

||||

| サンプリングCLK | 0.66ns ~ 5ms ※0.33ns(3GHz)は未サポート | ||||

| LVDS部 高速多CH同時性能 |

250Mbps/5CH ※暫定値 現在検証装置を拡充している都合で、ここまでしか検証できておりません 10CH時、20CH時の性能は随時アップしていきます |

||||

| CLK最大分析周波数 |

|

||||

| 計測振幅電圧 |

|

8CH単位

| 0-4 CH (5CH) | LVDS用 ツイスト線で、P/N差動で接続します |

| 5-7CH (3CH) | CMOS用 単線で接続します スレショルド固定。振幅範囲1.5-3.3V |

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |