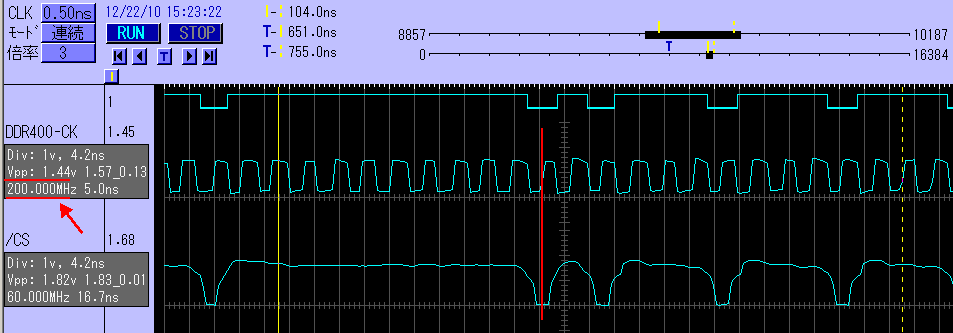

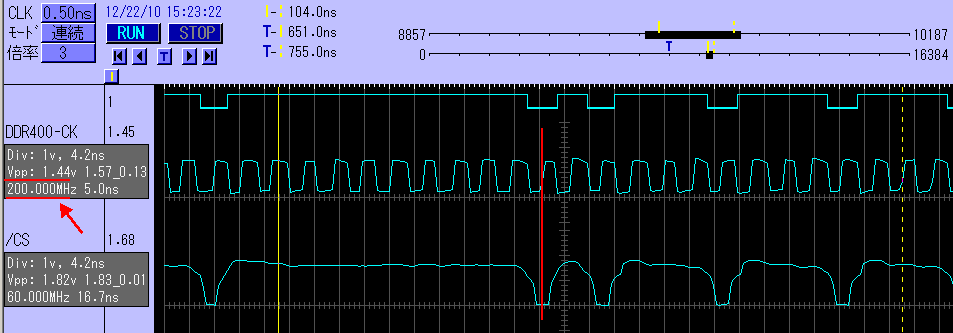

DDR2-400 400Mbps, 200MHz

この測定はFPGA出力信号を、DDR2メモリ直前で測定

DDR2-400のCLK と /CS

SSTL18-1.8V

CLK 200MHz、周期5ns

DDR2の振幅は、1.8V。実際は、CLKについては、±0.1の減衰があるので、1.8

- 0.2 = 1.6V の振幅になる。(-3dB) = 70%なので、

帯域幅200MHzを満足する振幅 1.6 × 70% =

1.12V

従って、1.12V 以上あれば計測器としての帯域幅は満足することになる。

この測定では、/CS は変化が遅いので充分。CLKも、Vpp

= 1.44V 。帯域は充分満足している。HL-Dutyもほぼ良い。

上図赤線部分では、CLKと/CSの位相差が的確な位置で確認できています。

帯域幅200MHzの検証ができています。

帯域幅

| LOSCL2B-DDR ※DDR2-400まで |

| CLK帯域幅 |

1CH:

2、3CH: |

200MHz (-3dB)

250MHz (-6dB)

170MHz (-3dB) |

| 単パルス帯域幅 |

1CH:

2、3CH: |

1.0ns, 500Mbps

1.25ns 400Mbps |

※200MHzは1CHのみ使用。2,3CHはその派生信号として使用

※DDR400での基本使用CHは1,2CHのみ。3CH同時使用の場合、3CHは変化の遅い信号が条件

※2,3CHの帯域幅170MHzはCLKに対する性能ですが、1bitパルスは、2.5ns

= 400Mbps まで分析可能です。 データ1bitはCLKと同じ変化レートなので連続変化は避けて下さい。1bitパルスとして、変化間隔を広げて下さい。(実例にて別途解説)

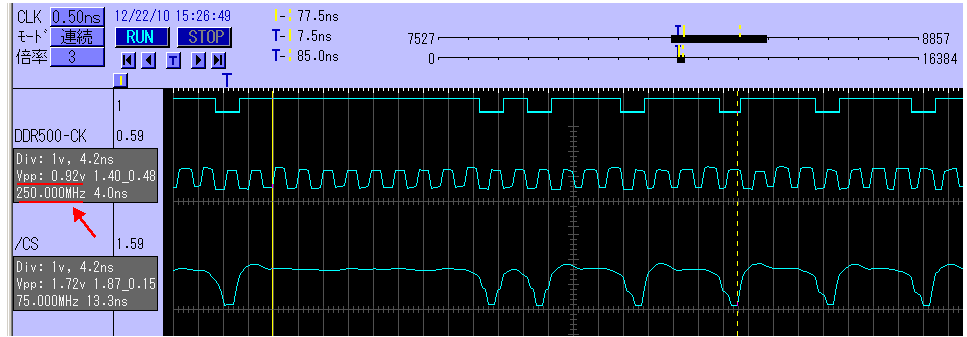

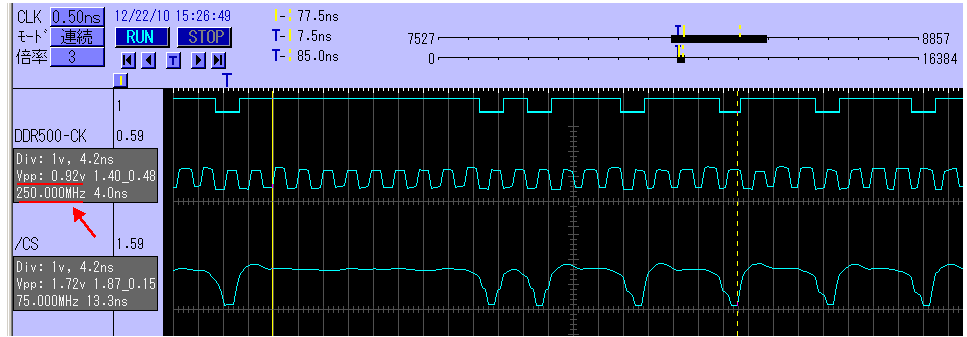

DDR2-500 ( 250MHz ) を測定すると (本機能の帯域幅は、200MHz(-3dB) なので、仕様を超えた参考例になります)

DDR2-500のCLK と /CS

SSTL18-1.8V

CLK 250MHz、周期4ns

DDR2の振幅は、前回同様、1.8 - 0.2 = 1.6V

の振幅として、(-6dB) = 50%なので、

1.6 × 50% = 0.8V

従って、0.8V 以上あれば、(-6dB)は満足することになる。Vpp = 0.92V が測定できていますのでそれは満足しています。

計測器としての帯域幅は(-3dB)は必要なので、(-6dB)のデータは参考数値として下さい。

なお、250MHzは、必ずしも分析できません。HLが潰れることも起きます。あくまで参考性能と考え下さい

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。

|

Copyright (c) デルタコア All Rights

Reserved.