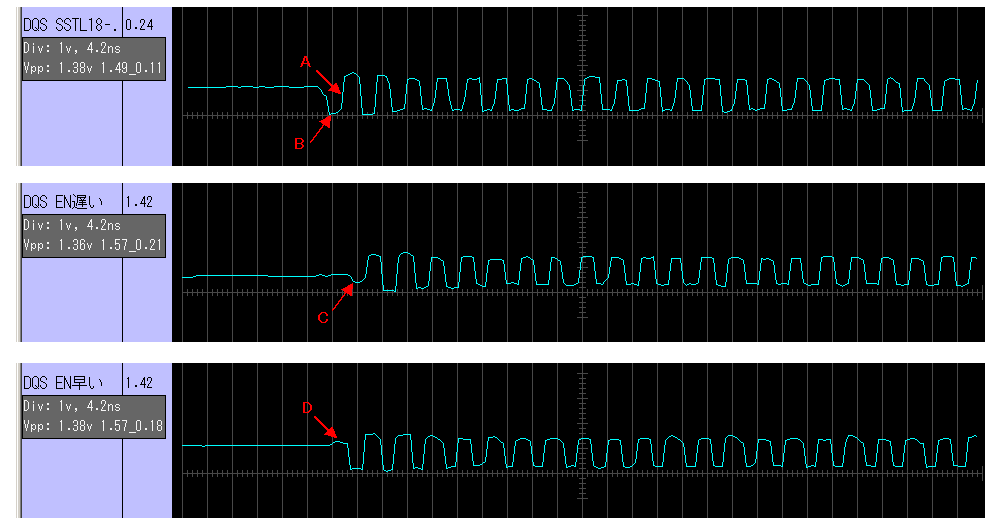

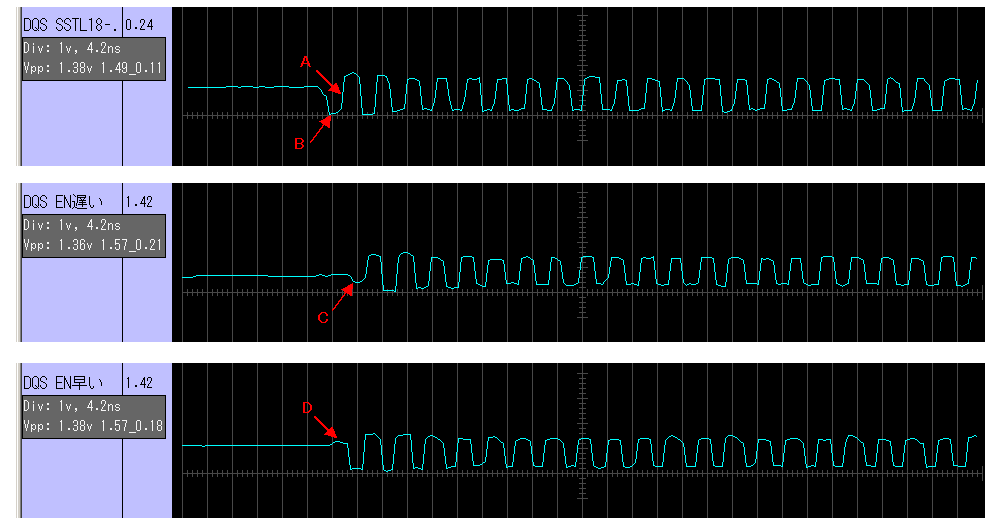

DQSのWR側で注意する点に、イネーブル制御があります。

データに対して90度先行させるため、通常、基本CLKに対してPLLなどで位相を作成します。

気をつけないとならないのは、DQS有効ウィンドウ内で開始しなければならず、かつ、双方向なので非アクティブHizから開始することです。

|

DDR2-400 |

DQS イネーブル |

DQSのWR側で注意する点に、イネーブル制御があります。

データに対して90度先行させるため、通常、基本CLKに対してPLLなどで位相を作成します。

気をつけないとならないのは、DQS有効ウィンドウ内で開始しなければならず、かつ、双方向なので非アクティブHizから開始することです。

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |