| FPGA-コア電源 | 1.2V |

| FPGA-IO電源 | 2.5V |

| DDR-コア電源 | 1.8V |

| DDR-REF電源 | 0.9V |

|

FPGA基板の電源の動的変化の分析 |

オプションLDSO用 |

安定したFPGA設計は回路設計だけでは不十分になり、電源設計の時代になりました

最近のFPGAを搭載した基板は、電源が複数になり、各低リプルが要求されます

コア電源は、リプル数10mV以下が要求されるようになり、電源設計が繊細になっています

高速シリアル用電源は更に繊細さが要求されています

測定で求められるのは、動的な電源状態を測定できるかです

・最大電力消費時

・短時間大電力変化時

どういう瞬間を測定するかは、ユーザのシステムに依存するので、測定者が考えなければなりませんが、

当LDSOは、要求に対応する機能があります

・低ノイズフロアで、業界稀な14bit-ADCの高分解能

・ロジアナ8CHが付属されており、ロジアナでトリガーし動的状態を特定できる。これは従来の2CHオシロではできません

・ロジアナのトリガーはグリッチ検出法に対応しており、サンプリングCLKを粗くしても、100Mbpsより高速のパルスを逃しません

・プローブ先端がICピンを直接掴める

【分析例】

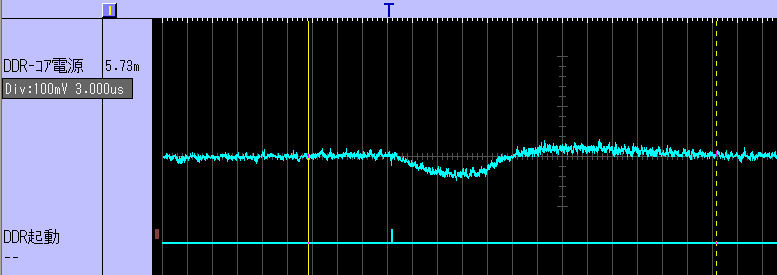

●DDR(SDRAM)メモリのコア電源 → アイドルから動作開始の瞬間

●FPGAのコア電源 → コンフィグ中に電源負担が変動する瞬間

DDR(SDRAM)メモリのコア電源 → アイドルから動作開始の瞬間

FPGA周辺のメモリの主流はDDR(SDRAM)ですが、それを例に実験します

|

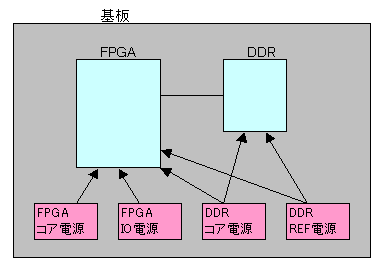

左は基板イメージです

|

DDRコア電源を対象にします

電力が最大変化するのは、アイドル状態から動作開始状態に移行する時です。

何をトリガーにするかは、ユーザのシステムに依存するので、測定者が考えなければなりません

当LDSOには要望に答えられる機能があります

この基板の場合、以下の信号がFPGA内にあるのでそれを使いました

外部モニターピンにアサインしロジアナで掴みます

| DDR起動 | DDR起動、アイドル状態から動作開始状態に移行する時にON |

| state[2..0] | DDR制御状態用の3bit (CH数、速度など) |

以上計4bit

測定条件

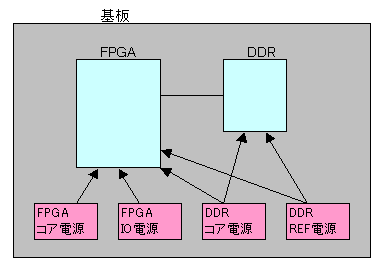

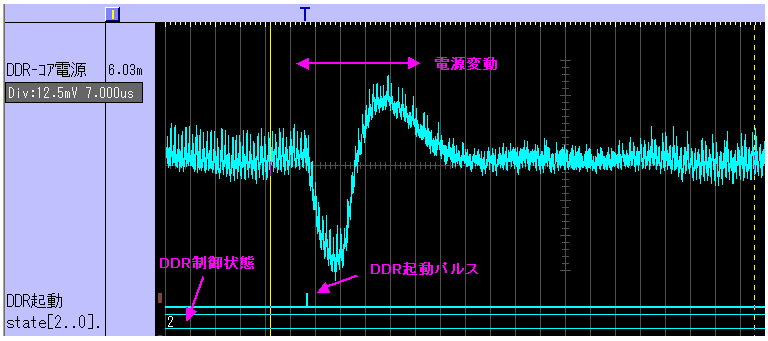

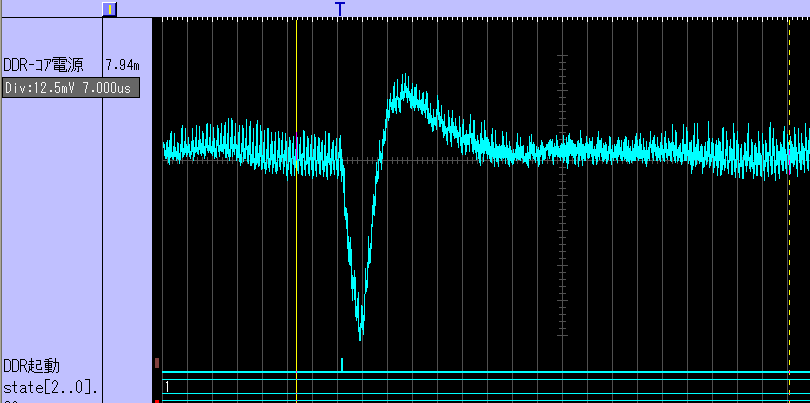

ACモード、倍率:1倍、Div:12.5mV、サンプリングCLK:20ns、分解能10bit+ロジアナ6ch

トリガー:DDR起動信号↑(グリッチ=ON *ONにすると、サンプリングCLKを粗くしても100Mbpsのパルスでも漏れなく捉えられる)

|

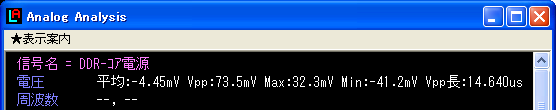

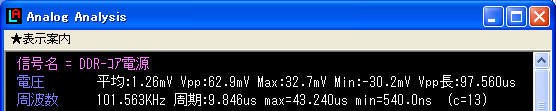

Vpp = 73.5mV、Vpp長 = 14.64us 気を付けないとならない水準の電源電圧変動の存在が分ります |

●DDR制御状態を変えてみます → CLKを遅くする

state = 5 に変化

|

Vpp = 62.9mV、Vpp長 = 97.56us Vppは減少しました |

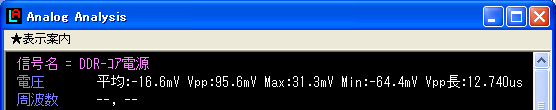

●DDR制御状態を変えてみます → CH数を多くする

state = 1 に変化

|

Vpp = 95.6mV、Vpp長 = 12.74us Vppは大幅に増加しました。危険です。電源対策が必要です。 |

測定ができれば、電源を対応することはいろいろできるはずです

レギュレータ容量、パワーFET感度、フェライトBZ容量、C容量、...

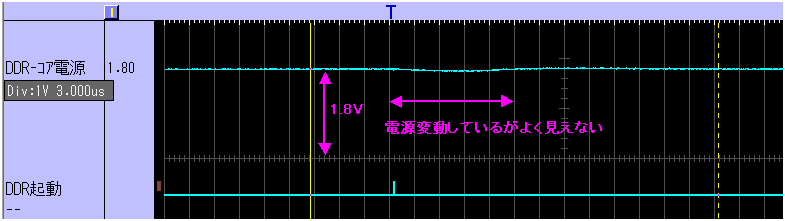

●ACモードにする訳

普通オシロの測定はDCモードですが、電源ノイズを見るときは、ACモードが適しています。

DCモードで見る場合、Divレンジをその電圧まで広げますが、するとmVレベルの大きさは見えなくなってしまいます

DCモードで実際に測定すると、

DDRコア電源は1.8Vなので。数10mVの変化は、上図のように微妙に変化する程度です

当LDSOは分解能14bitと業界最高レベルなので、拡大するとある程度見ることもできます。

(同じことを分解能8bit品でするとほとんどわかりません)

なお、分解能は14bit+ロジアナ2chに変えています

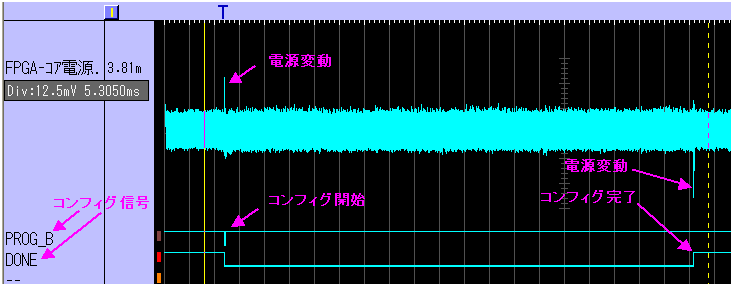

FPGAのコア電源 → コンフィグ中に電源負担が変動する瞬間

FPGAのコア電源は、最近の高速タイプは使用条件が厳しく、リプル数10mV以下が規定されています

高速シリアル用電源は更に繊細さが要求されています

作成する回路で電力が変動する原因は様々です

ここでは、コンフィグ中を取り上げます。実は知る人ぞ知る、FPGAコア電源はコンフィグ中にかなり変動します

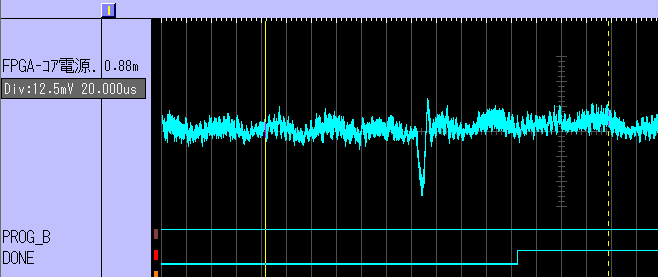

FPGA(XILINX)のコンフィグ信号の内、以下をロジアナで掴みます(説明はメーカーコンフィグマニュアル参照)

| PROG_B | コンフィグ起動 |

| DONE | コンフィグ中 |

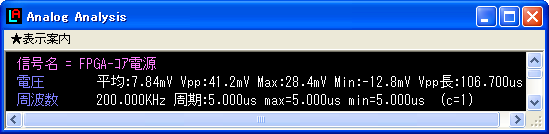

測定条件

ACモード、倍率:1倍、Div:12.5mV、サンプリングCLK:100ns、分解能10bit+ロジアナ6ch

トリガー:PROG_B↑(グリッチ=ON *ONにすると、サンプリングCLKを粗くしても100Mbpsのパルスでも漏れなく捉えられる)

|

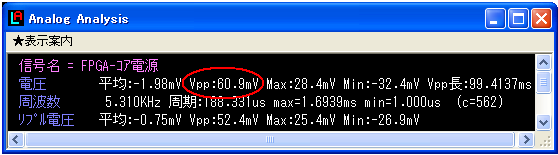

Vpp = 60.09mV コンフィグ中、FPGA-コア電源は変動しています |

★コンフィグ時間は約100msありますが、3Mサンプリングのメモリを使い全サンプリングできています。メモリは最大64MあるのでLDSOにとっては余裕です

★コンフィグ開始パルス(PROG_B)は、40nsなのでCLK=100nsにした普通のロジアナでは見えなくなりますが、グリッチ検出をONにしているので捉えています

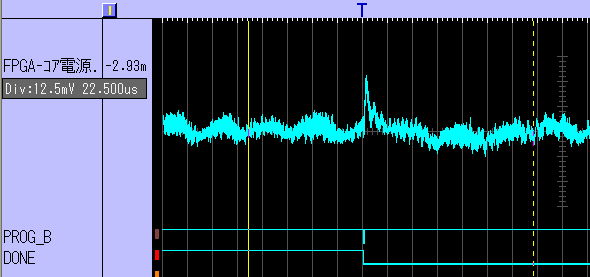

●コンフィグ開始時

|

Vpp = 41.25mV 再コンフィグ時、生成回路が解かれて、電力が極端に減るために電源が変動します |

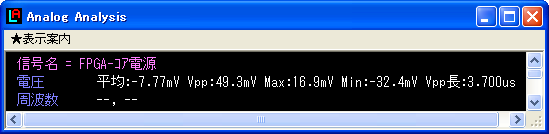

●コンフィグ完了時

|

Vpp = 49.3mV コンフィグ完了時、回路が生成される瞬間、電力が極端に増大します この影響は回路使用率が大きくなるほど大きくなるので注意が必要です |

大規模FPGA程、上の現象は顕著になるので、コンフィグが不安定になったら疑ってみることです

測定ができれば、電源を対応することはいろいろできるはずです

レギュレータ容量、パワーFET感度、フェライトBZ容量、C容量、...

FPGAのコア電源負担が変化する例

・大規模カウンタのイネーブル=ONの瞬間

・高速PLLの起動の瞬間

・並列モジュールが有り、通常1個起動だが、稀に多数個が同時起動する時が在り、その瞬間

起動信号とステータス信号を数bitロジアナで同時サンプリングすればそれらを捉えることが出来ます

コア電源の最大変動は、瞬間にのみ存在します。

それ以降は電力が高いままでもリプルは落ち着きます。だから、今動作しているからとただ測定しても最大リプルは測定できません。

|

※当ロジックアナライザーLogicMOTHERは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |