●サンプリング条件の調整

80Mbps以上になると、まず、サンプリング条件が合っているかを検証しなければなりません

調整箇所

| スレショルド電圧 |

高速になると、信号振幅電圧は、VCC電圧とは等しくならないので、一致する値を見つけなければなりません |

| 外部CLK位相 |

↑か↓。そこからの遅延0,1,2,3 |

●データ検証

テストパターンを発行させ、それをサンプリングし、化けのないことを検証します

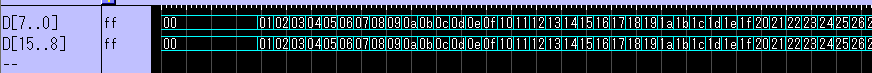

インクリメント・パターン

0101 から FFFF まで単純インクリメント

同時スイッチングノイズ誘引・パターン

インクリメント・パターンに続いて、同時スイッチングノイズ誘引・パターンを使います

0000 と FFFF が繰り返すパターンです

インクリメント・パターンはサンプリングは厳しくありません。同時スイッチングノイズ誘引・パターンこそが、検証で重要です。

Aが最もエラーになりやすく、Bもそこそこなりやすい

これがエラーにならなければ、サンプリング条件は合っていると言えます。

この検証を最低数10回し、データ化けが無いことを確認します。あれば上記調整(スレショルド、位相)をします。

これで回路に流れるデータをサンプリングできる環境になるわけです。

●テストパターンの検証ができなかった場合

1.基板のIFが不安定で本当にエラーしている

→測定する以前の設計の問題

2.基板のIFはギリギリ成立しているが、それを外部に引き出して測定することができないほど冗長度がない

→測定はできないことを意味します

150Mbpsの調整例(実例)

構成

| 構成 |

バッファ: LHBUF・E 2個

ケーブル: LIC-ESET 2個、LIC-E2SET 1個、LIC-DSET 1個 |

| 信号 |

CLK: 150MHz

DATA: UPエッジ同相16bit

VCC電圧: 3.3V |

設定

| スレショルド電圧 |

LHBUF・E は、VCC電圧=3.3V の場合、1.8V

スレショルド設定ダイヤログに”電圧入力値解説”の対応表参照 |

| 外部CLK位相 |

エッジ: UP ※1

遅延: 0 |

※1

データを同相で出力しているなら、逆相の方が良いように思えますが、100MHz超になると世界が違ってきます。サンプリングするとなるとセットアップタイムを満足する必要があり、同相の方が適することになります(難しく考えず位相を変えながら丁度良いところを見つければよい)

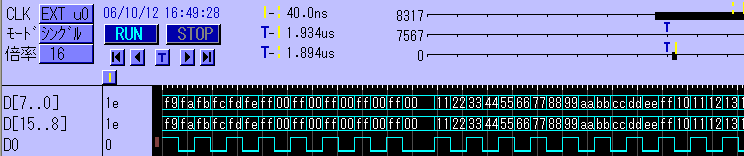

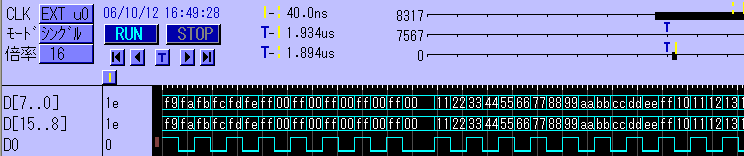

測定結果

同時スイッチングノイズ誘引・パターンが正しくサンプルできています

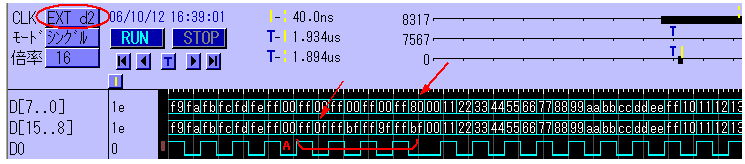

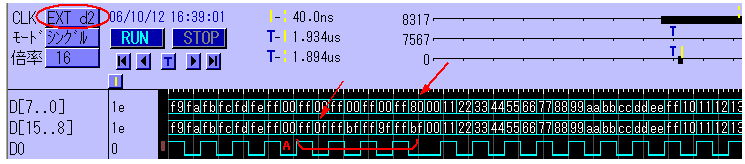

位相を変えてみます

CLK EXT u0 → EXT d2 (UPエッジ+0ns → DOWNエッジ+2ns)

A同時スイッチングノイズ誘引・パターン内が不規則に化けています

矢印のところは、00 でなければなりません

前後を見ると、化けているのは、同時スイッチングノイズ誘引・パターン内のみで、インクリメントパターンなどは正常です。

つまり検証は、同時スイッチングノイズ誘引・パターンを使用しなければ厳密にはできないということです

この検証では、位相は、以下の3遅延が正常になりました。

EXT u1 中央値+1

EXT u0 中央値、ベスト

EXT d3 中央値-1

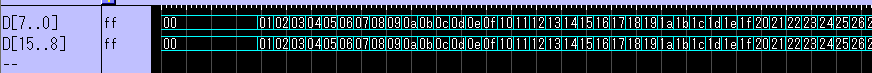

次に、スレショルド電圧を変えてみます

前8CHバッファだけ、1.8V → 2.2V

D[7..0] のみは、データ化けはなくなりました。信号振幅に問題がある回路なら効果が出ます

調整結果

| スレショルド電圧 |

1.8V |

| 外部CLK位相 |

EXT u0 |

これで調整ができましたので、以降、実際の回路に流れるデータの分析をして良いことになります

Copyright (c) デルタコア All Rights Reserved.