扨弮偵巊偆応崌丄杮懱夞楬偲SCANLOGI夞楬偼摨懍偺CLK偱偄偄偱偡丅

SCANLOGI夞楬偼偦偺傑傑偵奜偵捛壛偡傞宍偱丄

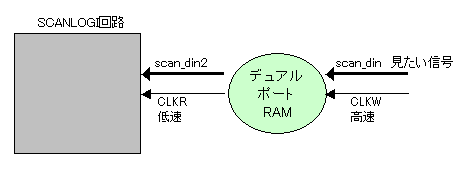

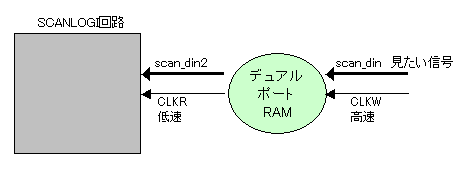

嵍恾偺傛偆偵丄娫偵僨儏傾儖億乕僩RAM傪偐傑偣傞偲丄僒儞僾儕儞僌CLKW偲庢傝弌偟CLKR偼暿偵偱偒傑偡丅

僨僶僀僗偑摦嶌偡傞側傜丄僒儞僾儕儞僌CLKW亖500MHz側偳傕壜擻偵側傞傢偗偱偡側傞傢偗偱偡

|

幚慔 |

偙偙偐傜幚慔揑偵偳偆巊偆偐傪愢柧偟傑偡

偙傟傑偱SCANLOGI夞楬傪夝愢偟偰偒傑偟偨偑丄幚偼偦傟偼婎杮偱偟偐偁傝傑偣傫

偦傟傪儀乕僗偵揥奐偑懡條偵偱偒傑偡

僒儞僾儖偼WEB偱悘帪岞奐偝傟偰偄傑偡

侾丏FPGA儊乕僇乕偺僣乕儖乮僠僢僾僗僐乕僾丄僔僌僫儖僞僢僾側偳偺撪晹怣崋愱梡乯摨條偺偙偲傕偱偒傞乛懍搙挷惍僶僢僼傽儕儞僌

PLD(FPGA)撪晹+奜晹儘僕傾僫偼丄婎杮偼儕傾儖僞僀儉僒儞僾儕儞僌側偺偱丄CH悢偑懡偔側傞偲丄僷儔僔儕曄姺偩偗偱偼僒儞僾儕儞僌偼侾乛CH偵抶偔側傝傑偡

偟偐偟丄SCANLOGI夞楬偺慜偵丄撪晹RAM傪晅偗偰僶僢僼傽儕儞僌偡傟偽丄僒儞僾儕儞僌CLK偲僷儔僔儕CLK偼暿偵偱偒傞偺偱僒儞僾儕儞僌CLK摨懍偱懡CH撪晹怣崋傪儊儌儕偱偒傑偡

偙偺曽朄偵偡傞偲丄FPGA儊乕僇乕偺僣乕儖乮僠僢僾僗僐乕僾丄僔僌僫儖僞僢僾側偳乯偲摨偠偙偲偑偱偒傞偙偲偵側傝傑偡丅偙偺帪傕奜晹怣崋傕僒儞僾儕儞僌偱偒傑偡丅

|

懍搙挷惍僶僢僼傽儕儞僌 扨弮偵巊偆応崌丄杮懱夞楬偲SCANLOGI夞楬偼摨懍偺CLK偱偄偄偱偡丅 SCANLOGI夞楬偼偦偺傑傑偵奜偵捛壛偡傞宍偱丄 嵍恾偺傛偆偵丄娫偵僨儏傾儖億乕僩RAM傪偐傑偣傞偲丄僒儞僾儕儞僌CLKW偲庢傝弌偟CLKR偼暿偵偱偒傑偡丅 僨僶僀僗偑摦嶌偡傞側傜丄僒儞僾儕儞僌CLKW亖500MHz側偳傕壜擻偵側傞傢偗偱偡側傞傢偗偱偡 |

俀丏僷儔僔儕帪娫傪儕傾儖帪娫偵偡傞

僷儔僔儕帪娫偼丄8bit側傜丄8攞CLK偐偐傞偺偱丄僒儞僾儖儗乕僩偼1/8偵側傝傑偡

偟偐偟丄偦偺暘僷儔僔儕CLK傪崅懍偵偡傟偽懍搙傪偦偺傑傑偵儕傾儖帪娫僒儞僾儕儞僌傕壜擻偱偡

椺

僔僗僥儉CLK=10MHz側傜丄僷儔僔儕CLK=80MHz偵偡傟偽丄撪晹怣崋偼寚偗傞偙偲側偔儕傾儖帪娫偱僷儔僔儕曄姺偟偰弌椡偱偒傑偡

俁丏LD怣崋傪棙梡偟尰徾傪摝偝側偄

僔僗僥儉CLK偲僷儔僔儕CLK偑摨懍偱傕丄儔僢僠偡傞偨傔偺儘乕僪怣崋丗LD乮scan_ld乯傪棙梡偡傟偽丄昁梫側怣崋偼偦傟側傝偵摝偝側偄偙偲偼壜擻偱偡

SCANLOGI夞楬偵偼LD怣崋乮scan_ld乯偑偁傝傑偡

|

嵟傕桳堄媊側棙梡朄 |

徻嵶儘僕僢僋偺専徹偼丄僔儈儏儗乕僔儑儞偱廩暘側偼偢偱偡

幚婡専徹偱壗偑媮傔傜傟傞偐

婎斅慡懱偺摦嶌丂偲丂FPGA撪晹忬懺丂偲偺僔儞僋儘忬懺

偙偺専徹偑幚婡専徹偺儊僀儞偵側傞偲峫偊傑偡

FPGA儊乕僇乕偺僣乕儖乮僠僢僾僗僐乕僾丄僔僌僫儖僞僢僾側偳乯偼傛偔棙梡偝傟傑偡偑埲壓偑偱偒傑偣傫

丒儊儌儕偑尷掕偝傟偰偄傞偺偱丄嬌彫扨埵偟偐尒傟側偄丅戝偒側忬懺慗堏偑尒傟側偄

丒FPGA偵庢傝崬傫偱偄側偄怣崋偼尒傟側偄乮婎斅慡懱偼尒傟側偄乯

偙偺PLD撪晹+奜晹儘僕傾僫偼丄偦偙偑偱偒傑偡乮慜弎偺傛偆偵FPGA儊乕僇乕偺僣乕儖偲摨偠偙偲傕偱偒傞乯

婎斅偺挿帪娫偺戝偒側忬懺慗堏傪丄FPGA撪晹偲FPGA偵愙懕偝傟偰偄側偄奜晹怣崋偲偱摨帪偵専徹偡傞

FPGA撪晹傪娷傫偩婎斅偺忬懺慗堏傪寁應偱偒傞傕偺偼懚嵼偟偰偄側偄丄偦傟偑偙偺曽朄偱偼偱偒傞偲偄偆偙偲偱偡

|

仸摉儘僕僢僋傾僫儔僀僓乕偼丄僨儖僞僐傾幮僆儕僕僫儖奐敪偱偡丅

婰嵹偝傟偰偄傞奺柤徧丄惢昳柤偼丄奺幮偺彜昗丄傑偨偼丄搊榐彜昗偱偡丅 |