先端キャップは外しダイレクト接続

|

波形形状分析(中速) |

オプション: LOSCL4 |

LOSCLは高速CLKを分析できるだけではなく、波形形状分析も優れていることを説明します

アナログオシロ(帯域100MHz)で、27MHzを見ます。その後当機LOSCLで同じ測定をして、その結果を比較します。

・FPGA(xilinx-virtex)、I/O指定 CMOS2.5V、ドライブ電流=デフォルト12mA

・基板終端 1KΩプルダウン

FPGAはドライブ電流を可変できるので、変えて比較して見ます

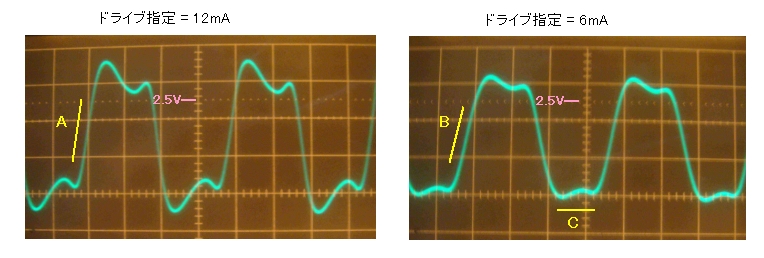

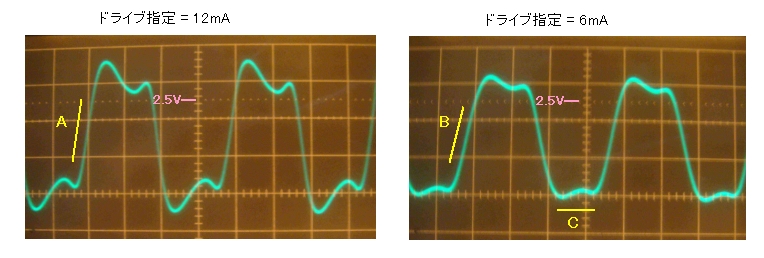

●一般アナログオシロ(帯域100MHz)

見慣れたアナログ波形だと思います

普通のオシロでは27MHzといえばこれ以上に分析できるものはお目にかかれないはずです

|

Div: 1V, 10ns 先端キャップは外しダイレクト接続 |

注目点

・波形エッジ角度、印A、Bを見ると、印Bは鈍り過ぎに見える

・両方Vpp=3Vを超えている。CMOS2.5V指定なので、オーバーシュートがある

この結果で、果たして、どちらのドライブ指定が適正なのか?

12mAの方は、過剰振幅が強い。6mAの方は、エッジが鈍っていて、印CのLow幅が狭過ぎて見える

どちらのドライブ指定が適正なのかはなんともいえないと思います

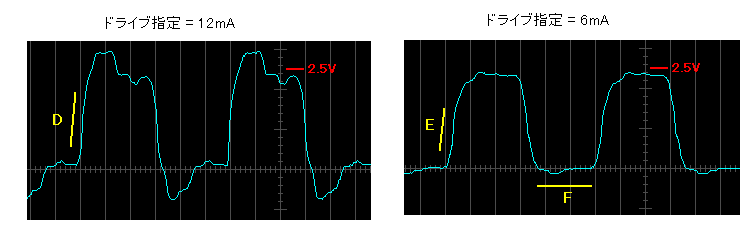

●当機LOSCL

同じ信号を、当機で見るとどうなるか。見えなかったものが見えてきます

|

Div: 1V, 6.3ns ICクリップ接続 |

注目点

・波形エッジ角度、印D、Eを見ると、共に鋭角で、アナログオシロの印Bのような鈍りは確認できない

・12mAの方は、オーバーシュートが有るが、6mAの方は無い

・印FのLow部は十分な幅が確認できる

この結果で、明白に、6mAのドライブ指定が適正だと確認できます

また、12mAの方の全般形状をアナログオシロと比較すると、変化点の信号の暴れ方がより詳細にわかります。

如何に12mAが過剰ドライブなのかがわかります。(この実測環境の場合)

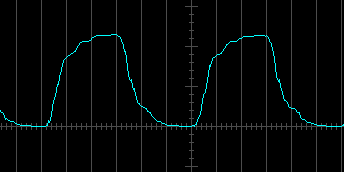

4mA指定したときを計測すると以下です

本物の鈍りが確認できます。これだと接続側によってはドライブ指定が少し足りないかもしれません

| ドライブ指定 = 4mA | ||

|

Div: 1V, 6.3ns ICクリップ接続 |

評

FPGAが持つドライブ電流可変機能は、実はオーバーシュート部分が影響することだとわかります。

”ドライブ電流 = 6mA”の波形エッジ角度は鋭角で、オーバーシュートも無い。

つまり、理想的にドライブされたので、この基板終端とマッチングされ余分な電力が消費されない為と考えられます。

FPGAのデフォルト電流指定12mAは、数I/O同時に高速に接続できるようドライブに余裕があるということです

しかし、接続数、速度によっては、デフォルト指定のままだと、それは余分電力となり、波形のゆがみ源、基板のノイズ源として加算されてしまうということです

重要なCLK信号は、この分析をして、適切なドライブ電流指定をして基板の更なる安定化を目指しましょう

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |