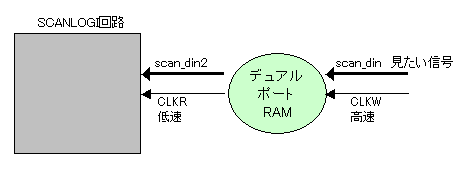

単純に使う場合、本体回路とSCANLOGI回路は同速のCLKでいいですが、高速に連続でサンプリングしたいなら、

左図のように、SCANLOGI回路はそのままに、中間にブロックRAMをかませると、

サンプリングCLKWと取り出しCLKRは別にできます。

デバイスが動作するなら、サンプリングCLKW=500MHzなどの高速も可能になるわけですなるわけです

|

モード:RAM法 |

速度調整バッファリングをすることで、デバイスが動作するなら、500MHz以上でも内部サンプリングが可能になります

FPGAメーカーなどが提供しているツールの原理と同じです

この方式は更に、FPGA外部信号も同時にサンプリングできます

(事前に、SCANLOGI回路を理解しておいて下さい)

|

速度調整バッファリング 単純に使う場合、本体回路とSCANLOGI回路は同速のCLKでいいですが、高速に連続でサンプリングしたいなら、 左図のように、SCANLOGI回路はそのままに、中間にブロックRAMをかませると、 サンプリングCLKWと取り出しCLKRは別にできます。 デバイスが動作するなら、サンプリングCLKW=500MHzなどの高速も可能になるわけですなるわけです |

中間にデュアルポートRAMをかませる方法は単純なHDLですので、自己流でできると思いますが、ここで作ったものを公開します。汎用構造にしていますので自由にお使い下さい

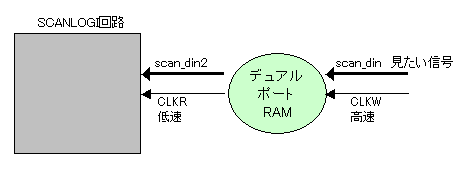

ブロック図

SCANLOGI_buf回路:

・ SCANLOGI_B(SCANLOGI基本回路)にd_mem(ブロックRAM)を付けて関係をまとめたもの

・速度調整バッファリングをする場合、これを共通に使えます

※SCANLOGI_Bとは、添付回路のSCANLOGIとほぼ同じですが、LD信号出力が最初から出るところを変えました

| CLKW | サンプリングCLK。 デバイスが動作するなら速度無制限高速可 |

| CLKR | ロジアナの取出しCLK |

| RST(図中略) | 内部で使用されるRSTと同じで構いません。アクティブlow |

| scan_en | サンプリング開始(トリガー)を作ります。Hi有効。サンプリング中、Hiホールド必要。次回のサンプリング開始時は、Low解除必要 rd_endをみてリセットすれば、再サンプリング開始ができる (CLKW同期) |

| rd_end | バッファリングデータがロジアナへ出力し終わったことを知らせる、パルスHi有効 CLKW同期) |

| scan_din | サンプリング信号を入力 最大256CHまで CLKW同期) |

| CKEXT | ロジアナへの外部CLK出力 |

| PLD_serdata | ロジアナへのシリアルデータ出力 |

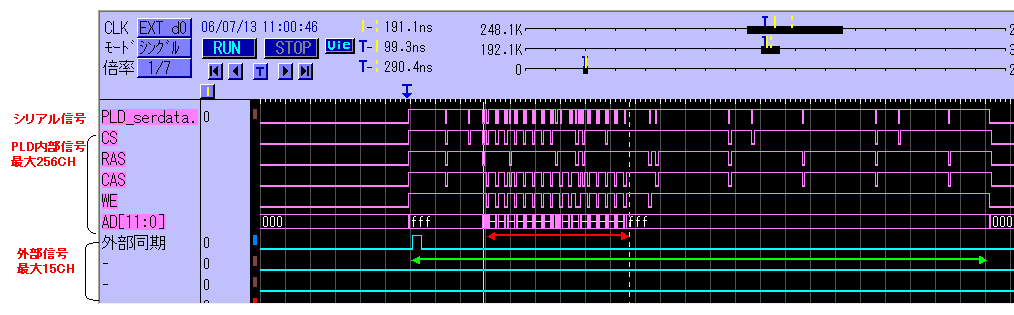

実際にFPGA内部のDDRメモリ制御をロジアナしてみます

DDR666Mのコントローラーと、FPGA外部の信号をロジアナします

| 内部サンプリングCLK | 333MHz(DDR666) |

| 取出しCLK | 20MHz |

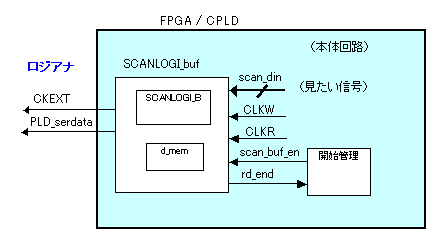

RUN:サンプリング実行

デュアルポートRAMサイズ=256にしているのでその幅(緑矢印区間)のサンプリングをしています。FPGA内部だけでなく、外部同期の信号も同時にサンプリングできています。

このDDR制御を簡単に説明します。赤矢印区間がデータアクセスで、以外はREFサイクルです。RAS,CAS,ADは複数DDR共通使用なので、ここのCS以外の位置でもアサートされています

デュアルポートRAMサイズはこのように対象現象に合わせて作成すれば良いわけです

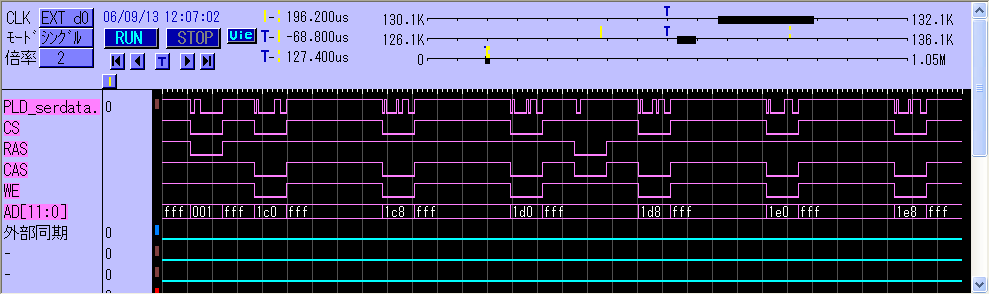

上は倍率=1/7なので、拡大すればAD値も以下のように完全にbitレベルで分ります

ファイルの説明

| ファイル名 | 説明 |

| SCANLOGI_buf.VHD | SCANLOGI_B.VHDに、ブロックRAMを付けて、サンプリングと取り出しCLKを分離できるようにしたもの ブロックRAMは、FPGA固有のものにする必要があります。例が添付されていますので使用するFPGAに合わせて合成ツールで作って下さい。 RAM以外はそのまま使えます。 |

| SCANLOGI_B.VHD | SCANLOGI回路基本部分、そそまま使えます |

| d_mem | デバイスに合わせて、合成ツールで作ったブロックRAM このRAMは使用するデバイスで作成して下さい、添付されていません |

本体回路に、SCANLOGI_bufを接続

本体回路に、componentを挿入して、見たい信号を接続します

本体回路

| entity TOP is port ( ・・・ CKEXT :out std_logic; -- ロジアナ外部CLK PLD_serdata :out std_logic -- ロジアナシリアルデータ ); end TOP; 略(component宣言など) --component接続 SCANLOGI_1: SCANLOGI_buf generic map(BLEN => 16) --サンプリングbit幅指定、16=16bit --RAMの物理サイズとは別に停止ADRを指定できるわけです port map ( CLKW => CLK_DDR666M, --サンプリングCLK CLKR => CLK_20M, --取出CLK RST => RST, scan_en => scan_en, --サンプリング開始 scan_din => scan_din, --サンプリングデータ CKEXT => CKEXT, --ロジアナ外部CLK PLD_serdata => PLD_serdata, -- ロジアナシリアルデータ rd_end => rd_end --取出完了 ); --サンプリング信号接続 scan_din <= so1_ad(11 downto 0) & so1_we & so1_cas & so1_ras & so1_cs1; --DDRの各種信号から見たいもの --サンプリング開始 --ここは個別の対応です、実際に合わせて下さい process( CLK_DDR666M, RST ) begin if (RST = '0') then scan_en <= '0'; elsif(CLK_DDR666M'event and CLK_DDR666M='1') then if(f_sdram_wr = CLR) then --DDR完了でCLR scan_en <= '0'; elsif(rd_end = SET) then --ロジアナ取り出し終了でCLR scan_en <= '0'; elsif(drv_sdram_wr_p = SET) then --DDR起動でSET scan_en <= '1'; else scan_en <= scan_en; end if; end if; end process; |

※構造の基本は別インデックス: デモカウンタ8bit、シミュレーション を読んで下さい

ブロックRAMの作り方

ここでは、xilinxのCORE generatorを使用しました。メーカーによって何でも良いですが、以下の要点を合わせて下さい。

COMPONENT d_mem --名称(何でも良い) PORT ( clka : IN STD_LOGIC; ena : IN STD_LOGIC; wea : IN STD_LOGIC_VECTOR(0 DOWNTO 0); addra : IN STD_LOGIC_VECTOR(7 DOWNTO 0); dina : IN STD_LOGIC_VECTOR(15 DOWNTO 0); clkb : IN STD_LOGIC; enb : IN STD_LOGIC; addrb : IN STD_LOGIC_VECTOR(7 DOWNTO 0); doutb : OUT STD_LOGIC_VECTOR(15 DOWNTO 0) ); END COMPONENT; |

要点

CORE generatorISE14.7の場合

Simple Dual Port RAMを選択(WRとRDでCLKが2系統ある1ポートのブロックRAM)

デフォルトからの変更点

・データ幅:16bit

・ADR幅:256

・ポートイネーブル有り

※データ幅、ADR幅、サンプリングしたい信号によってカスタマイズして下さい

SCANLOGI_buf.vhd の説明

この内部に、ブロックRAMのd_mem が使用されています。

FPGAに合わせたd_memにして、component宣言、component接続 を書き換えます

いじるところはそのブロックRAMだけです。

SCANLOGI_buf.VHD

-- 宣言 COMPONENT d_mem PORT ( clka : IN STD_LOGIC; ena : IN STD_LOGIC; wea : IN STD_LOGIC_VECTOR(0 DOWNTO 0); addra : IN STD_LOGIC_VECTOR(7 DOWNTO 0); dina : IN STD_LOGIC_VECTOR(15 DOWNTO 0); clkb : IN STD_LOGIC; enb : IN STD_LOGIC; addrb : IN STD_LOGIC_VECTOR(7 DOWNTO 0); doutb : OUT STD_LOGIC_VECTOR(15 DOWNTO 0) ); END COMPONENT; -- ブロックRAM接続 SCANRAM: d_mem port map ( clka => CLKW, ena => ram_w_en, wea => ram_w_we, addra => ram_w_adr, dina => scan_din, clkb => CLKR, enb => ram_r_en, addrb => ram_r_adr, doutb => scan_din2 ); |

component宣言は、ツールが吐き出すテンプレートそのままで大丈夫です

component接続は、同じ信号名をブラックボックス的に接続するだけです。

ブロックRAM:d_memは、デュアルポートRAMとしてメーカーツールが作成しますので、どのメーカーでも項目は同じになると思いますが、青字の信号名は微妙に違ってきます。

そのため、SCANLOGI_buf.VHD はコピーして使用できず、この部分だけは手動で書き換える必要があります。

外部信号と内部信号との遅延

速度調整バッファリングをすると、外部信号から内部信号はかなり遅延してサンプリングされることになります

同期ポイントで外部信号と内部信号は同期します。そこからサンプリングが進むと、以下の合算でどんどん遅延が加算されます

・シリパラ比

・サンプリングCLKと取り出しCLKの比

従って、同期ポイントから時間が経過するほど遅延が大きくなります

速度調整バッファリングは原理的にそうなりますので、外部信号との位置関係は、同期ポイントだけが合っていると理解下さい

時間の設定

外部CLKの場合このメニューの”周期設定”で時間単位を設定します。しかし、この機能は注意があります

内部と外部でCLKを変えているためです。従って、2カーソルで時間を測定する時、測定用途でその都度 ”周期設定” を変えることが必要です

| 内部信号(DDR666M) | 0.187ns (シリパラ16bitなので333M/16) | |

| 外部信号(20M) | 50ns | |

複数ドライブの間隔を測定する場合は、外部信号で周期設定して2カーソルで時間を測定します

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |