更に発展した使用法があります

同一サンプリング中に指定現象のみを何度もサンプリングできます

これにより、現象の発生間隔、連続性、がわかります

これも、チップスコープ、シグナルタップなど(各社商標)ではできない機能です

前インデックスの、”モード;RAM法” のファイル例をそのまま使用します

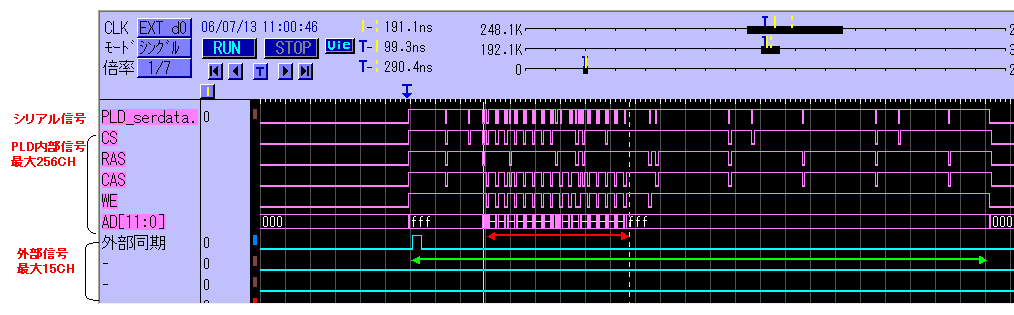

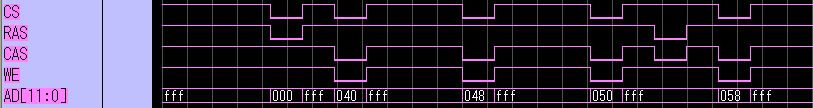

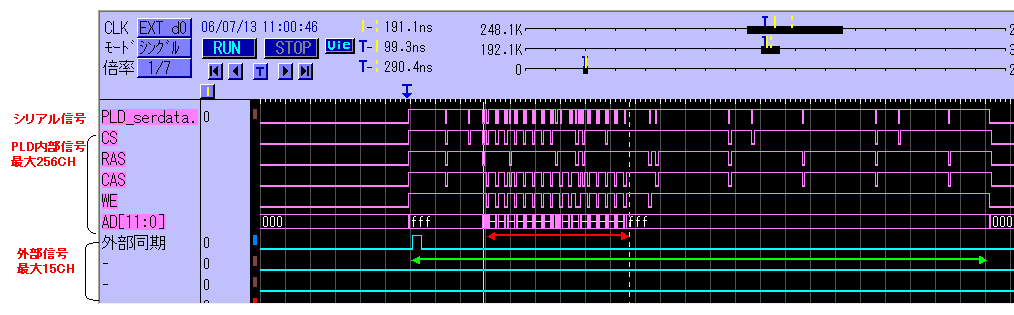

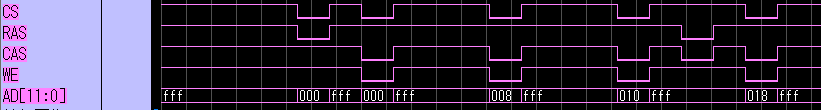

以下は、DDRドライブのサンプリングです(このDDRドライバは128バーストが1単位)

通常この方式(チップスコープ、シグナルタップなど)は、狭い時間を見ることに用途が限定されています。

サンプリングのためにFPGAの内部に作るRAMの幅はデバイスにより限界があり通常数10Kです。次の現象(DDRドライブ)が間隔が空いていれば、RAM幅が足りなくて見えません。

赤矢印区間がデータアクセスで、緑矢印区間がサンプリング幅です。デュアルポートRAMサイズ=256にしましたがその幅です。

1回のDDRドライブを見るにはこれで充分です

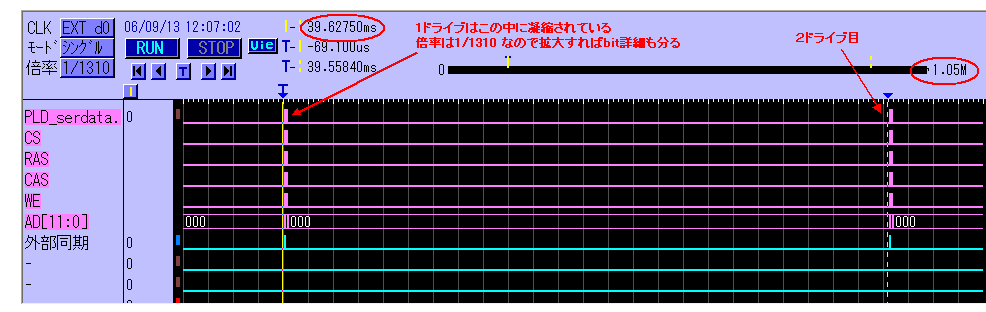

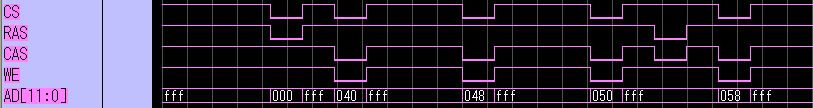

ところが当機能は、2回目のDDRドライブも連続でサンプリング可能なのです

最大64M/chの大容量ロジアナとの結合機能なのでそれが可能なのです

同じデュアルポートRAMが、格納がリセットされ、再利用されています

FPGAの残RAMが少なくても、容量が何倍にも拡大されているのと同じです

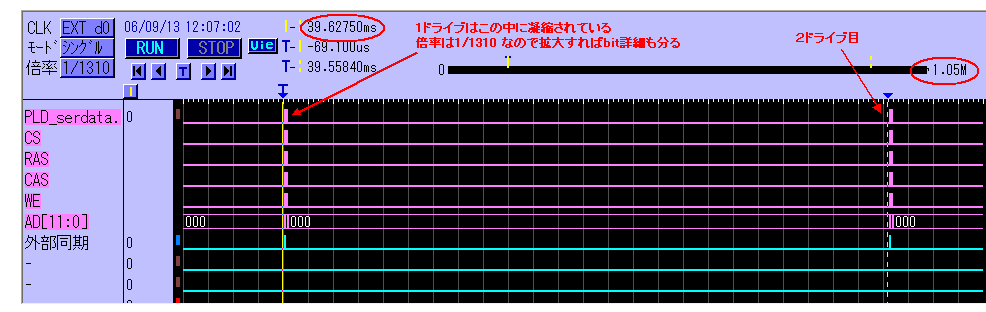

2回のドライブ間隔は、赤丸印内に表示されていますが、

39.6275ms

FPGA内のRAMを使う方式だけでは絶対に実現できない幅です

しかも、ここはロジアナのメモリ幅は1M使ってますが、最大この64倍まで更に幅を増やすことが可能です。3回目以降のドライブの連続状態もサンプリングできます。

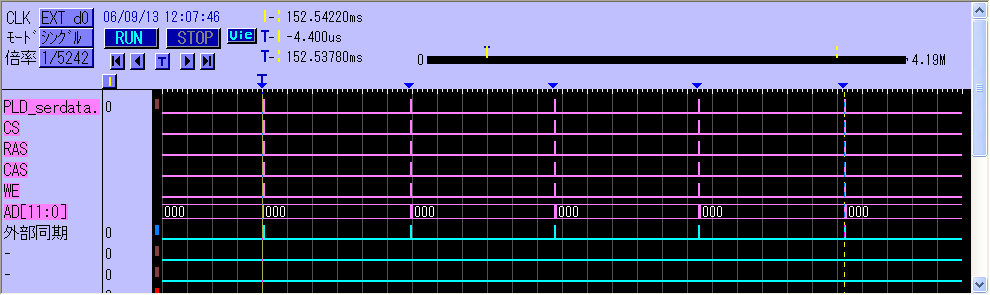

メモリ幅を4Mにしたのが以下です。5回の連続ドライブの状態がサンプリングできています。1-5回の間隔は、152ms

。これだけ長時間にわたるDDR全アクセスをサンプリングできたわけです

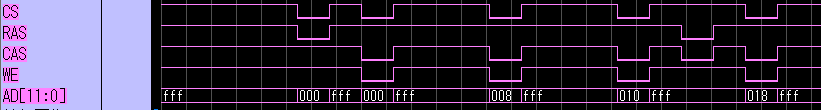

このDDRドライブは、回数ごとに128バースト単位でADRが更新します、各回を拡大してADRを見るとその通りになっているのが確認できます

|

1回目

000-000 → 000-018 ..(000-03F)

※BL=8なので8間隔

|

|

2回目

000-040 → 000-058 ..(000-07F) |

時間の設定

外部CLKの場合このメニューの”周期設定”で時間単位を設定します。しかし、この機能は注意があります

内部と外部でCLKを変えているためです。従って、2カーソルで時間を測定する時、測定用途でその都度 ”周期設定” を変えることが必要です

| 内部信号(DDR666M) |

0.187ns (シリパラ16bitなので333M/16)

※333Mは、DDR666Mなので半分。16は信号幅 |

| 外部信号(20M) |

50ns |

複数ドライブの間隔を測定する場合は、外部信号で周期設定して2カーソルで時間を測定します

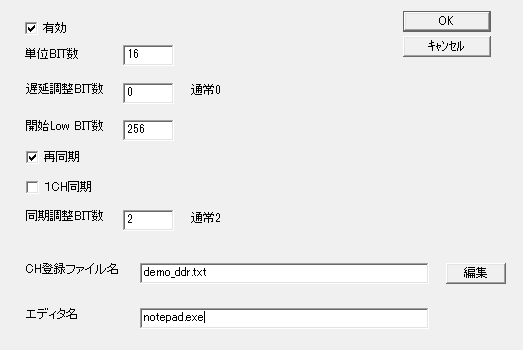

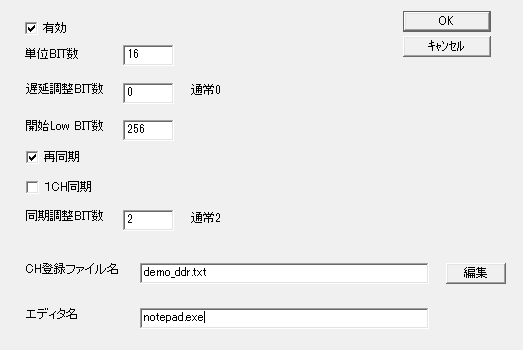

機能有効設定

連続現象を見るには、以下の設定を有効にします

| メニュー |

→ |

”ツール” |

→ |

”PLD内部外部ロジアナ” |

|

|

設定ダイヤログで、”再同期” を有効にします

注意:”再同期”は同期ポイント(11101)を再検索するので、実際にデータ中に同期ポイントがあるとそこで再同期してしまいます。そういう場合は、”開始LowBIT数”を大きくすれば偶然に再同期する確立が下がり回避できるはずです

|

また、本体回路にSCANLOGI_buf回路を挿入した際、以下の”サンプリング開始”を作っています

rd_end で、リセットされていることも2回目のドライブをサンプリングするには必要です。

--サンプリング開始

--ここは個別の対応です、自由に作成下さい

process( CLK_DDR666M, RST ) begin

if (RST = '0') then

scan_en <= '0';

elsif(CLK_DDR666M'event and CLK_DDR666M='1') then

if(f_sdram_wr = CLR) then --DDR完了でCLR

scan_en <= '0';

elsif(rd_end = SET) then --ロジアナ取り出し終了でCLR

scan_en <= '0';

elsif(drv_sdram_wr_p = SET) then --DDR起動でSET

scan_en <= '1';

else

scan_en <= scan_en;

end if;

end if;

end process;

|

トリガー

CH0の”PLD_serdata"に対してかけてます

トリガーの使用法は通常のロジアナと同じです。”PLD_serdata" "0 -> 1"

で立ち上がりエッジでかけます

”開始保持”を有効にして”50” が設定されているのは、データ列の中に、"0 -> 1" が含まれるのでそこで誤トリガーさせないためです。

”PLD_serdata" の先頭の "0 ->

1" でのみトリガーが有効になります。

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。

|

|

Copyright (c) デルタコア All Rights

Reserved.