リアルセレクタ法とは

当ロジアナは、高速ロジアナがベースなので、高速外部CLKで、RAMバッファを経由せず、リアルに内部をスキャンすることができます。

つまり、FPGA 内/外 の信号を、完全同期で同時にロジアナするということです

JTAG方式(遅い)ではできないオリジナルなFPGAロジアナの方法です。

FPGA内部RAMを使用していないので、サンプル数にFPGA残RAMの制限が無い

リアルセレクタ法 → 完全リアルセレクタ、状態リアルセレクタ

完全リアルセレクタ

-------------------------------------------------

-- SCANLOGI接続

-------------------------------------------------

CKEXT <= CK80M; --外部CLK

SCANLOGI_1: SCANLOGI

generic map(BLEN => 8) -- bit幅、16bitなら16

port map

(

CK => CK80M, -- 10MHzの8倍CLK

RST => RST,

scan_en => scan_en,

scan_din => scan_din, --10MHzで動作する8CHの内部信号

PLD_serdata => PLD_serdata,

scan_ld => scan_ld

);

|

例えば、10MHzで動作する8CHの内部信号をロジアナしたいとします。

8倍の80MHzの外部CLKがあれば、8CHの信号をリアルタイムで漏れなくシリアル出力できます

scan_dinに内部信号を接続し、その信号が10MHz動作なら、CK80M

= 80MHzを作成し、SCANLOGI回路に入力します。

CKEXTもCK80Mを接続します。

scan_en は適当にトリガーを入力し、scan_ld

は使う必要はありません

※CK80Mは、内部CLKと同期して作成すれば(DLL,PLL使用で普通に同期します)、scan_dinの位相合わせは要りません、単に接続でOK

状態リアルセレクタ

完全リアルセレクタは、動作CLKが10MHz以下ぐらいなら有効なのですが、高速になると限界があります。

別に状態をモニターするという用途があります。これは、動作CLKが高速でも、有効に使えますので説明します

例えば、FPGAの内部ステータス状態が、FPGA外の基板の信号とどうリンク動作しているかを見たい

こんな用途もあるときがあります

内部ステータス状態は、通常大きな時間幅で遷移するので、それほど高速でなくても良い場合があります

-------------------------------------------------

-- SCANLOGI接続

-------------------------------------------------

CKEXT <= CK; --外部CLK

SCANLOGI_2: SCANLOGI

generic map(BLEN => 6) -- bit幅、16bitなら16

port map

(

CK => CK,

RST => RST,

scan_en => scan_en,

scan_din => monitor, --6bitの状態信号

PLD_serdata => PLD_serdata,

scan_ld => scan_ld

);

-------------------------------------------------

-- monitor[5..0]:状態

-- status[3..0]:あるステータス

-- enbnk:あるイネーブル信号

-- drvpuls:ある起動puls

-------------------------------------------------

monitor <= drvpuls & enbnk & status(3

downto 0);

|

monitor[5..0] は、内部ステータスなどを結合したものです。CKに対して、大きな時間幅で変化すると考えてください。

これが、FPGA外の基板の信号とどうリンク動作しているかを見たい、という用途だと考えて下さい

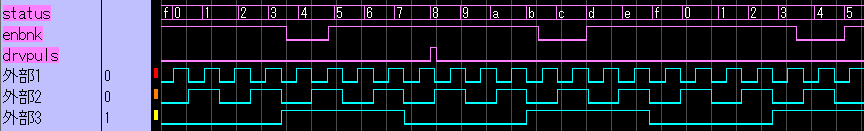

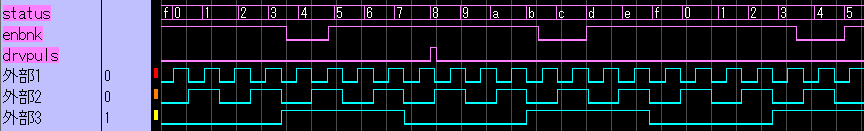

実行すると

monitor[5..0] の構成の内、status、enbnk、は、大きな時間幅で変化しているので、そのまま接続してもこうして見れます

しかし、実は、drvpuls は、CKの1bit幅しかありません。

scan_din が 6bit 幅だと、波形は、最小幅も6itになります。なので、drvpulsも1bit幅でも、6bit幅になります。

その発生場所は、外部ロジアナと同期しています

外部1,2,3という信号は、FPGAに接続されていない外の任意な信号を同時にロジアナしたものです。FPGA内部信号と完全同期しています

**************************

重要な補足:パルス信号のラッチ

**************************

scan_din を 6bit と定義した場合、その幅より小さい信号は、ただ接続すると見えたり見えなくなったりします。

その場合、scan_ld でラッチします。ラッチしても波形表示の幅は上の波形drvpulsと同じです。

drvpuls をラッチして接続する方法を解説します

-- monitor <= drvpuls & enbnk &

status(3 downto 0); -- 元のラッチ無し

monitor <= drv_hold & enbnk & status(3 downto 0); -- drvplusの変わりに、drv_hold を使用してSCANLOGI回路に接続する

-------------------------------------------------

-- 起動信号ラッチ幅確保

-- scan_din幅以下の信号は、単に接続しても確実に見れないのでscan_din幅まで拡大する

-- IN:drvplus

-- out:drv_hold

-------------------------------------------------

process ( CK, scan_en ) begin -- scan_enでRSTしてないと、scan_en有効前に、drv=ONしていると、

--scan_en有効で最初にその過去のdrvが1回出る

if (scan_en = '0') then

drv_pre <= CLR;

drv_hold <= CLR;

elsif (CK'event and CK = '1') then

if( drvplus = SET ) then -- 1CK幅の信号の場合、これでscan_din幅まで拡大する

drv_pre <= CLR;

drv_hold <= SET;

elsif( drv_hold = SET) and (scan_ld =

SET) then --scan_ldの1CLK後まで保持

drv_pre <= SET;

drv_hold <= drv_hold;

elsif( drv_pre = SET) then --hold解除

drv_pre <= CLR;

drv_hold <= CLR;

else

drv_pre <= CLR;

drv_hold <= drv_hold;

end if;

end if;

end process;

|

scan_din の幅より小さい信号は、このHDLをそのままコピーペーストして使って下さい

複雑に見えますが、ブラックボックス的に使って下さい。(詳細動作を解析したい方はシミュレーションして下さい)

*****************************

大きな時間幅で変化する信号の注意

*****************************

status、enbnk、は、大きな時間幅で変化しているので、そのまま接続しても見れますが、注意があります

アサート位置は、scan_din幅6bitに対してどこになるかは決まっていません。従って、本来の幅にscan_din幅6bitの揺らぎ(0から6bit)が加算されます。

つまりその揺らぎ分は大まかな変化の波形になるということです。

ここが”状態リアルセレクタ”が”完全リアルセレクタ”と違う点です

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。

|

Copyright (c) デルタコア All Rights

Reserved.