アナログ: 1CH

ロジアナ: 8CH

LDSO 2個まで可

|

電源電圧の分析 |

オプションLDSO用 |

安定したFPGA設計は回路設計だけでは不十分になり、電源設計の時代になりました

最近のFPGAを搭載した基板は、電源が複数になり、各低リプルが要求されます

FPGAコア電源は、リプル数10mV以下が要求されるようになり、電源設計が繊細になっています

高速シリアル用電源は更に繊細さが要求されています

LDSOは電源電圧分析用の特徴を持ちます

・高分解能 14bit-ADC

・ロジアナ8CH付き(動的現象特定)

・最大メモリ64Mサンプル

・低ノイズフロア

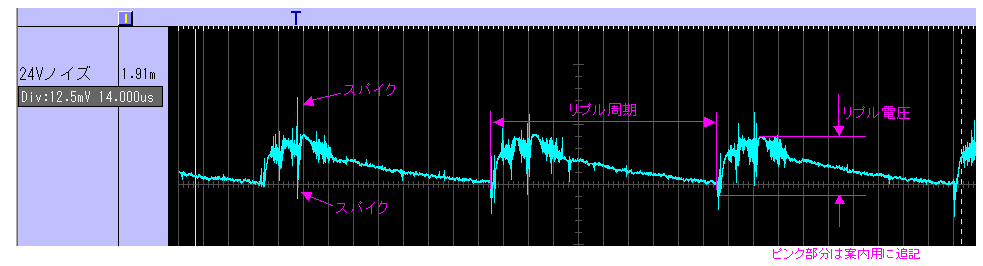

●スイッチング電源電圧の分析

基本の説明

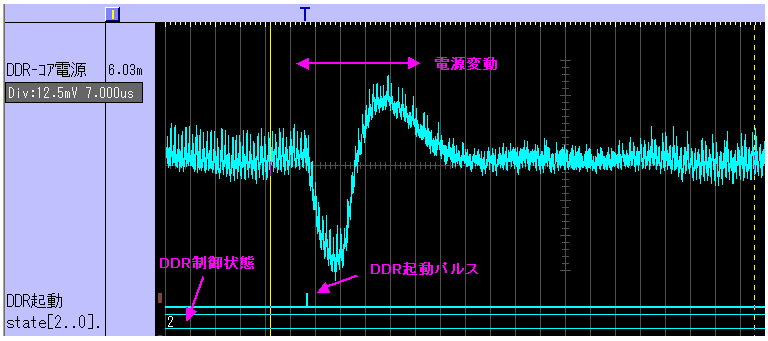

●FPGA基板の電源の動的分析

・DDR(SDSRAM)メモリのコア電源 → アイドルから動作開始の瞬間

・FPGAのコア電源 → コンフィグ中に電源負担が変動する瞬間

| LDSO2: ストレージオシロバッファ | ||

|

LDSO 1個で アナログ: 1CH ロジアナ: 8CH LDSO 2個まで可 |

スイッチング電源電圧に関する以下の項目が分析できる 詳細

|

FPGA電源電圧変動を動的に特定 詳細

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |