※イネーブルは、有効=Lowで固定しています(ソースの変更可)、未使用CHはLowになるので全有効になります

サンプリングCLKは、CLKの幅(片振幅)に対して、4倍以上の高速にして下さい

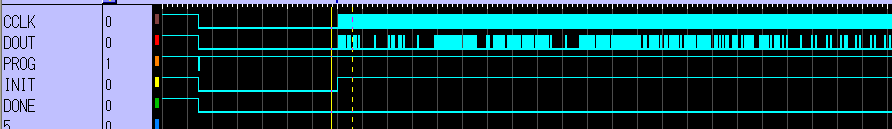

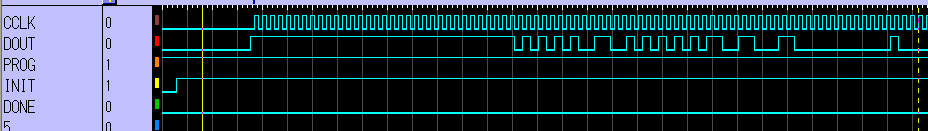

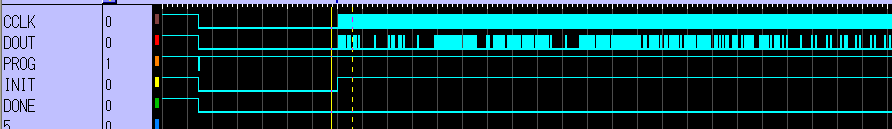

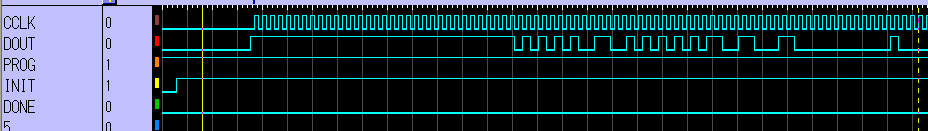

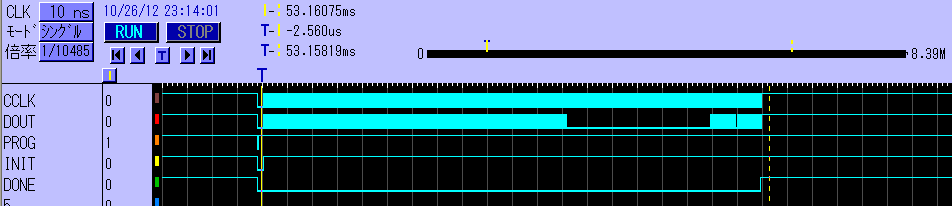

FPGAのコンフィグ信号をサンプリングしました(デバイス:Virtex2)

拡大

コンフィグ信号のCCLKとDOUTはCLK同期信号ですので、これをバイナリーファイルにしてみます。(DONEはコンフィグ時Lowなので、全有効になります)

|

シリアル分析ツール バイナリーデータ合成 |

汎用のシリアル分析でも可能だったですが、バイナリーファイルにできるツールを作りました

アドイン機能を利用しますので、ユーザにてカスタマイズ改造も可能です

FPGAのコンフィグ信号をサンプリングしてみます

1.サンプリング

CLK同期のCLKとDATA、の2信号をサンプリングします

分析ツールが、以下のch位置を使うように出来ていますので合わせて下さい

| 信号名 | ロジアナCH |

| CLK | CH0 |

| DATA | CH1 |

| イネーブル | CH4 |

※イネーブルは、有効=Lowで固定しています(ソースの変更可)、未使用CHはLowになるので全有効になります

サンプリングCLKは、CLKの幅(片振幅)に対して、4倍以上の高速にして下さい

FPGAのコンフィグ信号をサンプリングしました(デバイス:Virtex2)

拡大

コンフィグ信号のCCLKとDOUTはCLK同期信号ですので、これをバイナリーファイルにしてみます。(DONEはコンフィグ時Lowなので、全有効になります)

| ツール信号名 | ロジアナCH | コンフィグ信号名 |

| CLK | CH0 | CCLK |

| DATA | CH1 | DOUT |

| イネーブル | CH4 | DONE |

2.分析

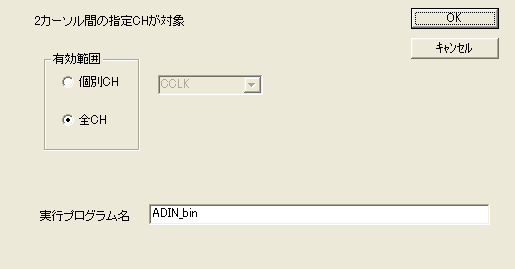

2カーソルで適当に囲み、分析をかけます。

メニュー → 分析 → アドインプログラム

|

有効範囲 = 全CH

|

|

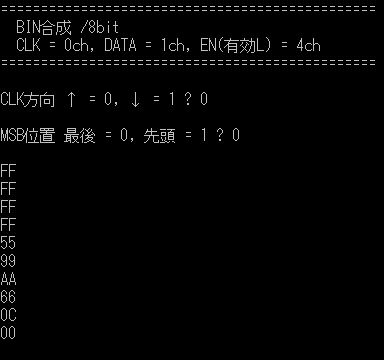

CLKの方向と、MSB位置を選択します FPGAコンフィグはほぼ決まっています CLK = ↑、MSB = 最後 2カーソル範囲のバイナリーデコードが表示されます 範囲はどこから始めてもOKですが、先頭がBYTE境界からずれるとbitずれします |

デコード範囲が大きいと、コマンドプロンプト画面では前半表示が消えていきます

広範囲を見る場合、テキストがフルで同時に作成されていますのでそちらをご覧下さい

| テキストファイル | bincvt.txt |

| バイナリーファイル | bincvt.bin |

3.コンフィグROMデータのフル合成(デコード)

当ロジアナはメモリが膨大にあることを使って、コンフィグデータをフル合成(デコード)してみます

メモリをある程度大きくして、シリアルデータが終わるところまでサンプリングします

ここは、メモリ幅8M、サンプルレート10ns、時間53ms でサンプリングできました

2カーソルをその両端に移動させ、

同じく、メニュー → 分析 → アドインプログラム

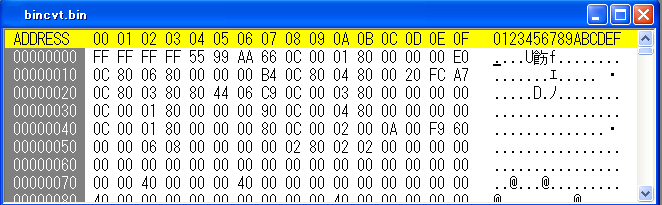

|

合成された bincvt.bin の先頭のダンプ |

作成された、bincvt.bin は、160Kbyte ( 1.28Mbit ) です

4.自由な改造

ソースが公開されてますので、自由に改造下さい

かなりコメントはあるし、難易度はそれほどではありません

| コンパイラ | VC6のVC++ |

| プロジェクトタイプ | win32 console application |

| メインソース | ADIN_bin.cpp |

マイクロソフトの旧式のコンパイラで、現在のコンパイラで読み込ませるとアップデートしてくれます。他社製でもいけると思います。

ダウンロード WEB → アドイン

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |