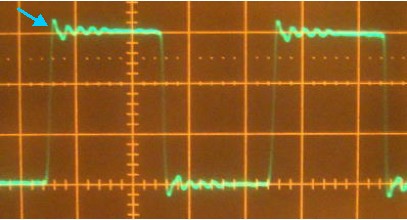

普通のオシロは、先端が細かいところが掴めないので、よくこのような細工をする方を見かけます

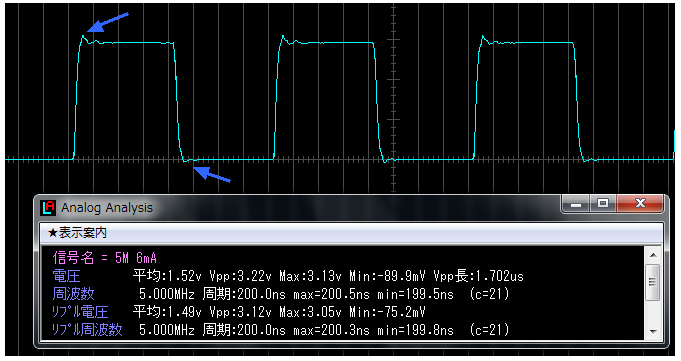

しかし波形は、変化点で、約5段に波打つリンギング青矢印が見られます。

リンギングとは、反射や特性インピーダンス不整合によって起きる波状ノイズです。特徴として波が徐々に減衰します参照

このリンギングは、プローブ部分が創作していることを説明していきます (本物のリンギングは存在します、別話です)

DIV: 1v, 50ns

| 新次元プローブの実力 | LOSCL使用 |

| 当社が開発した新次元プローブ 従来型プローブのウソの波形をあばく、リンギングはプローブが創作していた? (本物のリンギングは存在します、別話です) |

|

●概要

プローブは新開発しています。その特性を見ます

同軸プローブ: LBUF-PB

普通のアナログオシロのプローブより良い特性が出ていることを説明します

●試験環境

FPGA使用(VIRTEX4)

速度:5MHz

IO電圧: 3.0V

IO規格: CMOS

ドライブ電流: 6mA ※FPGAは可変できる

終端: 直列2KΩでGND

5MHz の波形を、新開発したプローブを使ったオシロ等価サンプリングと、普通のアナログオシロとで測定を比較します

●普通のアナログオシロでの測定

ます、普通のオシロ(帯域幅100MHz)を使い、プローブの先端の条件を変えて幾つか測定します。右写真はその時のプローブ。形状に注意下さい

| 1.先端を延長 普通のオシロは、先端が細かいところが掴めないので、よくこのような細工をする方を見かけます しかし波形は、変化点で、約5段に波打つリンギング青矢印が見られます。 リンギングとは、反射や特性インピーダンス不整合によって起きる波状ノイズです。特徴として波が徐々に減衰します参照 このリンギングは、プローブ部分が創作していることを説明していきます (本物のリンギングは存在します、別話です) |

||

|

DIV: 1v, 50ns |

|

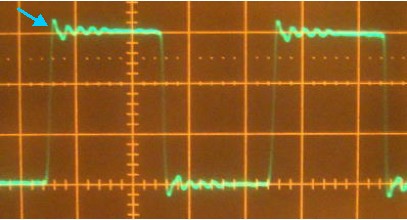

| 2.通常の先端 だいぶリンギングは収まっていますが残っています。 見慣れた波形なので信号とはそういうものと思っている方も多いと思いますが、本物の信号ではありません これが普通のオシロプローブの現実です |

||

|

DIV: 1v, 50ns |

|

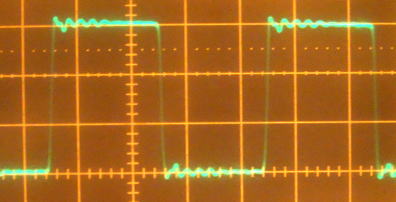

| 3.先端のキャップを外す リンギングはほとんどなくなりました。この方が特性が良く出ますが、先端を手で測定物に押さえ付けておかないとなりません。 これでも多少リンギングが残っているのは従来型プローブの構造的問題(GND部分が長すぎる)によるものです。 |

||

|

DIV: 1v, 50ns |

|

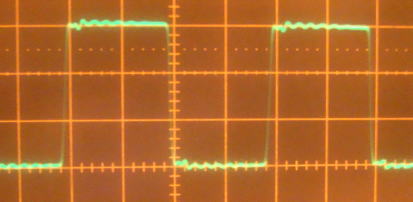

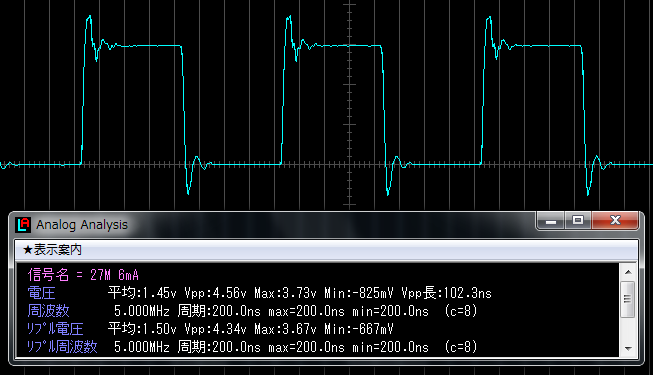

●当社が開発した新次元プローブでの測定 LOSCL 4GS/s

で測定

微小のオーバーシュート青矢印が観測されています。実際に存在するのはそれで、リンギングではないということです

この微小のオーバーシュートがアナログオシロで検出できなかった理由は、幅が3nsしかないため300Mbps超なのでアナログオシロの帯域幅を超えたためです

| 普通のオシロで良く見かけるリンギング、実際は存在しないのにプローブが内部で創作しているということです。 アクティブプローブでない限り、どのオシロでも程度の差はあっても起きます。機会のある方は試して見ると良いと思います 終端が悪いときなどに発生する本当のリンギングは存在します。それとは別の話です (この現象は、約1MHz - 10MHz で顕著に出現します) |

ここで、計測回路はそのままで、計測信号がFPGA出力なので、FPGAのドライブ電流指定を、 6mA → 12mA に変更して再測定してみます

今までとは計測信号自体が異なるので、別次元の話になります

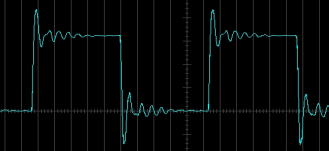

オーバーシュートが検出されました。本当に信号の乱れが存在すればそのように測定されます

信号が5MHzの低速で、1個の抵抗のみ接続されているので、12mAは過剰ドライブとなりオーバーシュートが起きています

オーバーシュートは大きいですが、段数は約2回で収まり、前記のアナログオシロが創作した5段に波打つリンギングにはなっていません

|

← 参考までに、本物のリンギングを測定するとこうなります 別の回路で測定しました 本当にリンギングがあればそれも正確に補足できるということです クリック拡大 |

なぜ、当方の開発のプローブは、創作リンギングが抑えられているか

プローブの構造が全く異なるためです

同軸プローブ: LBUF-PB

この解説中の写真を見て貰えればわかりますが、

すぐわかるのは、GNDケーブルの長さが違います。

(他の詳細は非公開です)

※GNDケーブルの長さはmm単位でオーダーできます

※先端にICクリップを装着することもできます

|

当方のプローブ先端は、ICクリップなのでICピンを直接つかめます 普通のオシロプローブの先端形状ですが ほぼ左です。 何10年前からその形です。想像するに開発当初はDIP部品しかなくそのもとに考案されたのでしょう。でも今時実用性はどうなんでしょう。そのフック形状で何を掴めっていうのでしょう。 キャップを外せばピンになっているので細部も当てられますが、手がふさがります。 |

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |