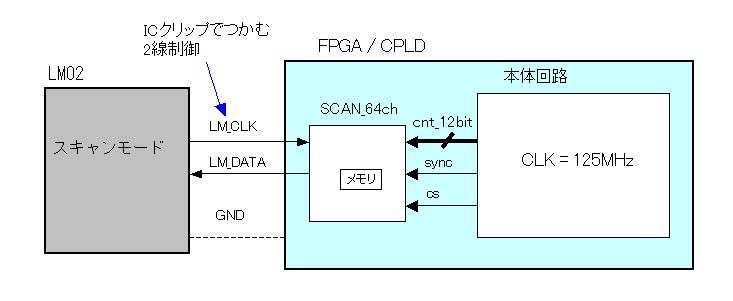

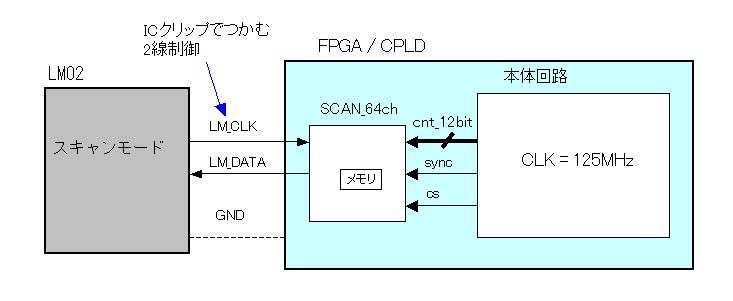

実使用例: CLK=125MHz内部同期 ” 16bit信号 + 単bit信号 ” のFPGA内部信号をスキャン

|

PLD内部スキャン |

FPGA内部デバッグの新基準を提案 更に進化したFPGA内部解析法 → FPGA内部外部ロジアナ |

| PLD(FPGA、CPLD)内に作成されたメモリ格納状況をスキャンする機能 利用法:内部信号状態、メモリの格納状況などのスキャン 2本の信号をICクリップケーブルでつかむだけで実現 |

|

| ●FPGA内部信号スキャン 任意の内部信号を割り当てれば、FPGA内部信号ロジアナのようになります 自由に作成したトリガー信号からの内部信号の動作を256CHまで観察できます |

実使用例: CLK=125MHz内部同期 ” 16bit信号 + 単bit信号 ” のFPGA内部信号をスキャン |

|

| cnt_12bit、cs、sync が今回スキャンする内部信号 |

| 方式 | ・SCAN回路は、VHDLコードをユーザーPLDに埋め込む方式なので、FPGAメーカー、デバイス、制限なし ・合成余りのリソースを使用 ・2信号必要。外出してある信号の余りがあれば自由に割り当てできます。ロジアナ付属のICクリップでつかむので特別なコネクター(JTAGなど)不要 ・回路合成は、各デバイスメーカーのツールを使用します。実行時は必要ありません ※VHDLコード、ロジアナ対応機能、1式提供されます。 ※VHDLはデバイスのサポートするメモリに合わせるためのカスタマイズが必要です(簡単にできるようにしてあります) |

| スペック | ・最大 256ch × 1MBit/ch ・内部CLK 500KHz以上が必要 (上限はデバイス動作可能まで。最近のデバイスは200MHz以上可能) ※合成余りのリソース容量に依存 |

| 必要構成 | 本機能自体無料オプションですが、ハード構成として以下が必要(ロジアナの基本構成と同じなので所有されていれば追加無し) ・LMBUF(標準バッファ)1個 ・ICクリップケーブルを1個 |

※2線式PLDスキャンの方式はデルタコア社オリジナル開発です。トランジスタ技術誌に技術広告を記載することで著作権を宣言

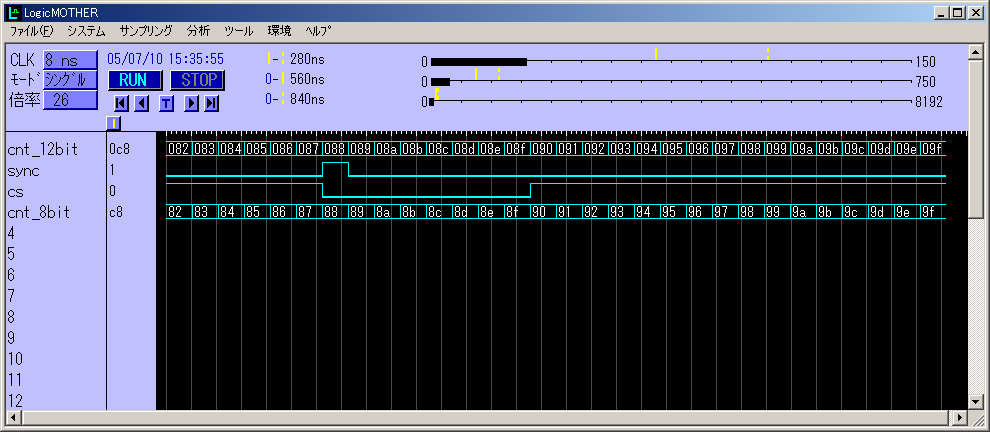

アプリ表示

VHDL解説

| SC: SCAN_64ch port map ( LM_CLK => LM_CLK, -- ロジアナIF: LM_CLK (in) LM_DATA => LM_DATA, -- ロジアナIF: LM_DATA (out) ----------------------- CLK => CK_125MHz, -- サンプリングCLK(任意) RST => RST, -- RST 有効-L (汎用の内部RST兼用でよい) ----------------------- smpl_en => smpl_en, -- サンプリング許可、有効-H smpl_sig0 => smpl_sig0, -- サンプリング信号 0-15ch smpl_sig1 => smpl_sig1, -- サンプリング信号 16-31ch smpl_sig2 => smpl_sig2, -- サンプリング信号 32-47ch smpl_sig3 => smpl_sig3, -- サンプリング信号 48-61ch smpl_busy => smpl_busy, -- 表示中、表示中は次のサンプリングできない、有効-H ----------------------- spml_dbg => scan_dbg -- リザーブ ); -- スキャンしたい信号を接続 smpl_sig0 <= "0000" & cnt_12bit; smpl_sig1 <= "00000000000000" & cs & sync ; smpl_sig2 <= "00000000" & cnt_8bit ; smpl_sig3 <= (others => '0'); |

以上は、portmap接続部分です。”SCAN”回路(名称:SCAN_64ch)のcomponent実体は、VHDLで完全に提供されます。

”SCAN”回路には、観測したい任意のPLD内部信号を自由に接続します。

トリガー信号は、 " smpl_en " に自由に作成したものを接続します

”SCAN”回路のVHDLは、ほとんどブラックボックスで使用できますが、使用するPLDデバイスがサポートするメモリを使用する必要があります。

詳細な解説が付属するので、HDLの基本がわかる程度で充分使用できます。

今回使用した、サンプルソース

smpl_c というカウンタから、スキャンする信号 cnt_12bit、cnt_8bit、cs、sync を単にデモ用にデコードして作成しているだけの簡単な回路です。

SCAN_64ch本体は、ユーザーに提供しております。

FPGAメーカーが提供している内部信号トレース機能との比較

| 当社のFPGA内部スキャン | FPGAメーカーが提供している内部信号トレース機能(当社の理解) | |

| FPGAメーカー | 全メーカー制限なし | 自社製品のみ |

| デバイス型番 | 実行時の型番制限なし、デバイスメーカーツール不要 (回路合成時はメーカー合成ツール必要) |

合成ツールとオプションのトレース機能の2つが必要 型番が大きくなると合成ツールは有料、トレース機能は無料/有料がある |

| コネクタ | 汎用IOを2信号のみ使用します。割当て信号位置は自由 バンク電圧は、1.5 ~ 3.5V (0.01V可変) |

JTAG |

| レア資料 | ・完全なHDLコードなので、通常の回路のようにメモリのプリミティブ選択、配置制約、周波数制約などができる。つまり、トレース機能を含めた本体回路全体で完全な合成制約ができる。 ・一度組み込めば、本体回路の修正合成でも組み込まれたままなので、トレース機能追加のための2度の合成は要らない。 ・組み込んだままコンフィグROM化できます。 |

トレース機能部分リソースのプリミティブ選択、配置制約のようなことは自由にできないと当社では理解しています。従って、内部検証用にリソースが入ることで動作周波数が低くなるなど発生する可能性があります。 |

※2010年5月の比較、FPGAメーカーの内部トレース機能はバリエーションが様々で当社の理解が正確でないところがあるかもしれません、その場合ご指摘下さい。

技術資料: LM_CLK信号制御 (LM_CLKは、ロジアナからPLDへ入力されるCLK信号名)

| スレショルド電圧 | FPGAのバンク電圧 1.5 ~ 3.5V (0.01V可変) |

| 終端 | 直列68オーム |

| 速度 | SCAN回路に接続する内部CLKは制限無し。LM_CLKは伝送用で、内部CLKとは別で低速独自シーケンス |

| ノンCLKエッジ | SCAN回路は、LM_CLKのCLKエッジを直接使用しない 伝送でCLKエッジが割れても対応できるように、内部CLKでダブルFFによるリタイミング 上記の理由から、CLK専用ピンに割り当てる必要はなく、ノーマルピンで可 |

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |