トップへ

(新しいページに情報が更新されています)

DDR-SDRAMサンプリング

|

高速メモリの代表である、DDR-SDRAMをサンプリングする方法を考察致します

当ロジックアナライザーでも、スピード的に、高速タイプDDR-SDRAMをリアルに対応することはできません

しかし、手法によって、分析できる方法がありますので、展開したいと思います |

| |

DDR400を分析するには、8点サンプリングとして、4Gクラスの測定器が必要になりますが高価です。

その測定器を用意できるのであれば問題はありません。しかし、DDR-SDRAM自体、高価な設備を持つ人しか使えない特殊なデバイスではないと考えます。中級な設備であっても、デバッグできるはずです。

当社のロジックアナライザーは、安価品の位置にありますが、それを使った、それなりのデバッグ方法をここに展開します。 |

ポイントは、問題の切り分けをすることです

| |

AC解析 |

|

→ |

|

各信号の位相差 |

|

|

|

|

|

|

| |

ロジック解析 |

|

→ |

|

コマンドの信号成分 |

|

|

|

|

|

コマンドの発生順番 |

|

|

|

|

|

クロックとのレイテンシ数 など |

|

|

|

|

|

|

| |

●AC解析

キーとなる信号は限られています。

CLKとコマンド、データの位相差、DQSとデータの位相差、などです。

それらは、一度測定し,調整が済めば、それ以上見る必要の無い作業です。(調整自体は神経使いますが)

そして、この作業は、アナログオシロ250Mhz程度のものでかなり間に合ってしまうと考えます。

アナログオシロ250Mhz程度なら、比較的一般的と思います。

DDR266までなら、当ロジアナの機能も利用できます 1.4GHzサンプリング(V2.7新機能) 、その2

●ロジック解析

デバッグで大変なのは実はこれです。DDR-SDRAMはかなり複雑なコマンド制御をするため、ここがデバッグのほとんどを費やすと思います。

ここで、当ロジックアナライザーをどう使うかを提案します。

それは、”DDRCLKを遅くする” です。

ロジック解析に限定するのであれば、基本的に、リアルなCLKスピードを使う必要は無いのです。

特に、コントローラーを製作しているのであれば、デバイスは、PLL付きのFPGAが多いはずです。

であるなら、PLLの出力CLKは簡単に1時的に変更することはできるはずです。

|

以上が、当社が提案する、問題の切り分けによる、DDR-SDRAMデバッグ法です。

以下、この手法による実測データを提示します。

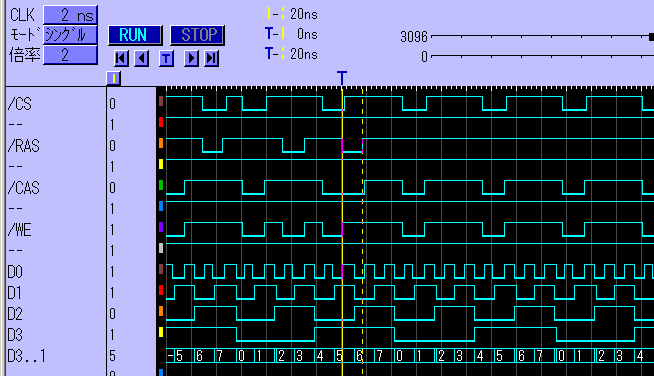

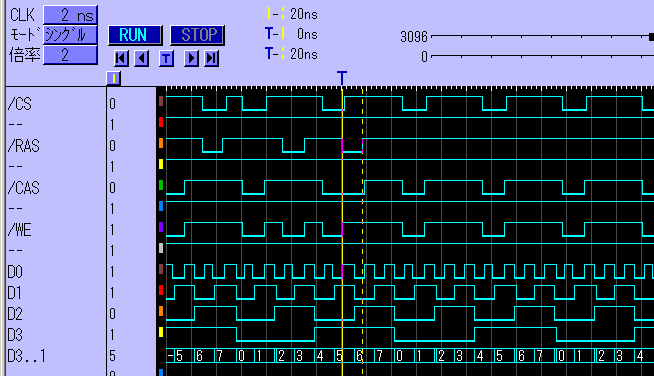

構成:

・DDR100(CLK=50MHz)まで速度を落とす

・低電圧高速BUF(LBH:オプション)使用。標準では、低電圧高速変化に適していないため。

・スレシュルド電圧 VCC=2.5V

・サンプリングCLK 500MHz

以上のように、CLKを遅くすることで、ロジック解析として実現できたと考えます。

カーソルの間を診ると、コマンド幅20ns(50MHz)、D0の変化単位はDDRなので2倍(100MHz)になっています。

AC解析が済んでいるなら、ロジック解析でデバッグが済めば、DDRCLKを戻しても動作できることになります。

(CLK、/CLK、DQSはコマンドの倍速で動作しているので入れていません。それらは、AC解析でのみ対象とします)

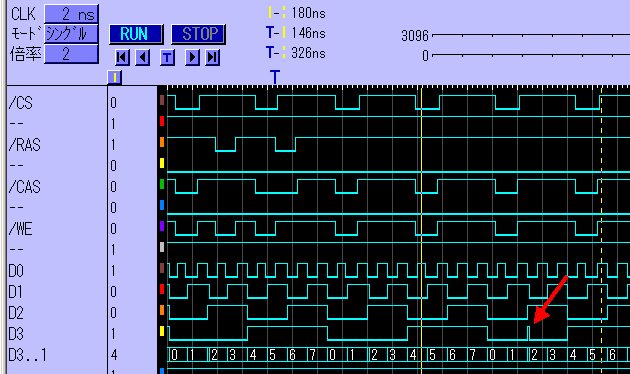

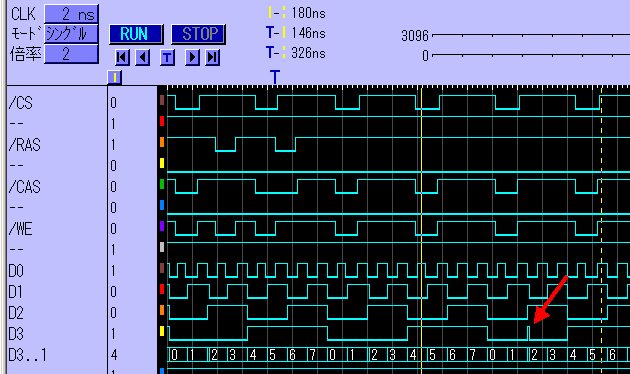

注意:ロジアナの宿命で同時スイッチングノイズがあります。

上例で、/CS、/RAS、/CAS、と1CH空けていますが、ノイズの影響を防ぐためです。

以下に、ノイズがある波形例を示します。

このように、高速多CH信号はロジアナにとって厳しい測定対象であることも注意下さい

|

※当ロジックアナライザーは、当社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。

|