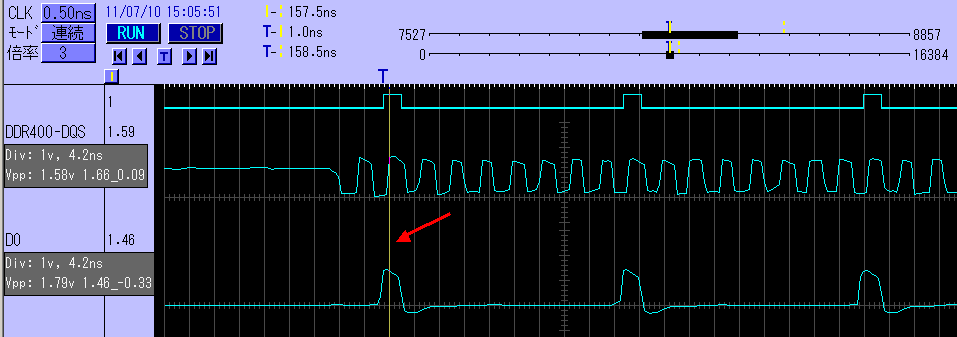

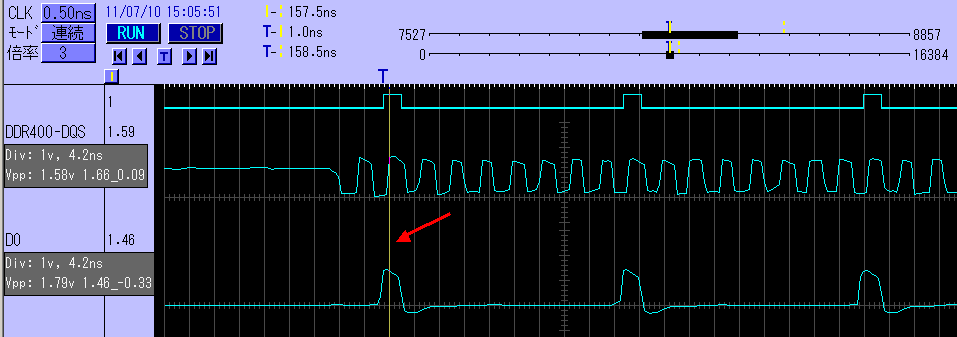

DDR2-400 400Mbps, 200MHz

|

DDR2-400 SDRAMの計測 |

|

| DDR2-400 データレート=400Mbps、CLK=200MHz | |

DDR400を分析開示しているのは パーソナル計測器で当製品のみ、アナログ/デジタル両方 ※高額な専用機以外確認できておりません。当社調査 2015/5

DDR2-400 400Mbps, 200MHz

DDR SDRAMの特徴

DDR SDRAM は、高速多容量メモリの主流であり近年FPGA制御の対象として広まっております。高額測定器が必要な理由から汎用エンジニアに浸透するネックになっている部分もあります。

DDR信号は、基板レベルで携わった方はおわかりですが、線路のインピーダンス制約、等長制約、特殊終端など、デリケートなIFです

従って、バス信号を多数本プロービングするなどは通常しません。ロジックのデバッグは、シミュレーション、デバイス内部スキャンなどで終了させます。

実測する部分は以下などになります。

・位相差

CLK/DQSと制御信号/データ間は、数nsで規定されており、その確認は通常高額な専用測定器を使用します

・アナログ的安定度

信号の終端が重要で波形形状に影響します。

電源ノイズは信号全般に波及します

・振幅電圧の確認

FPGAは、IOの電圧振幅レベルを選択できます。ファンアウトを考慮して規定しますが振幅電圧の実際の許容はアナログ波形を見る必要があります。

DDR2-400 分析の当機能でのデバッグコンセプト

DDR2-400 は当システムでも困難な速度領域になります。高額な専用機とは異なりますが、要点を分析できることに特化して構築しております。

CLKとCS、DQSとデータ のように、特定の2信号の位相関係を分析します

電源ノイズも分析可能です

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |