AD分解能14bit(業界希少) ※ほとんどのオシロは8bit

低ノイズ(業界最小水準) 実測ノイズフロア

メモリ最大64Mサンプル(業界最大水準)

帯域幅は普通以下ですので、高帯域幅ではLOSCLを選択下さい 当社デジタルオシロの分類

※電源ノイズ計測用にも特化されています

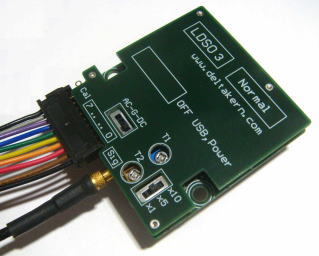

| 高解像度ストレージオシロ | オプション: LDSO3A |

アナログ屋さんのための、ノイズ測定に特化した高感度オシロ |

|

|

AD分解能14bit(業界希少) ※ほとんどのオシロは8bit 低ノイズ(業界最小水準) 実測ノイズフロア メモリ最大64Mサンプル(業界最大水準) 帯域幅は普通以下ですので、高帯域幅ではLOSCLを選択下さい 当社デジタルオシロの分類 ※電源ノイズ計測用にも特化されています |

|

説明 |

・スイッチング電源の解析 ※電源ノイズ計測用に特化されています

・FPGA基板の電源の動的分析

・FFT分析

●プローブの新しい形、新次元プローブ

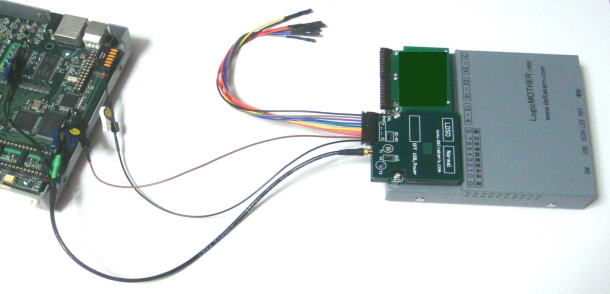

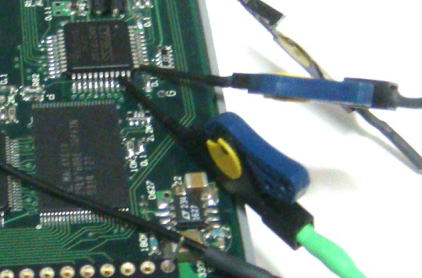

| プローブに特徴があります 普通のオシロのプローブは、約1.5m 、ロジアナとコンビで使用するには長さが合いません。先端形状もICピンはそのままでは掴めないものがほとんどです。当社で開発したオシロプローブは、約30cm なのでロジアナのICケーブルとコンビ測定可。0.8mmピッチICならそのまま掴めます。 (クリップは高精細タイプの別オプション有) |

普通のオシロの先端形状 |

|

|

|

| ロジアナとストレージオシロの同時測定、プローブの長さが合う | ICピンを直接測定 |

新次元プローブの実力、オシロ実測比較 (オシロ等価サンプリングLOSCLで比較) 注目 ※従来型プローブのウソの波形をあばく

●仕様

| サンプルレート、メモリ | 200MS/s、 5ns ~ 10us メモリ標準 1Mサンプル/CH、最大64Mサンプル/CH ※ロジアナの増設メモリが適用 |

||||

| AD分解能 | 14bit Div: 2mV - 10V |

||||

| CH構成 | アナログ1CH、ロジアナ8CH ※ 1個のLDSOに付き、最大2個装着可 切替: オシロ分解能14bit + ロジアナ2CH、オシロ分解能10bit + ロジアナ6CH、オシロ分解能8bit + ロジアナ8CH |

||||

| 帯域幅 | 3.3V CLKを対象 CLK50MHz (-9dB) ※-9dBとは、振幅が1/3。CLKの波形欠落無し CLK40MHz (-0dB) ※-0dBとは、振幅が100% ※帯域幅は普通以下ですので、高帯域幅ではLOSCLを選択下さい |

||||

| GNDノイズフロア |

|

||||

| 測定電圧、オシロ | -15 ~ +25v 誤差3% ※通電時耐圧 -20 ~ +30 V (AC/DC スライドSW切替) (プローブ倍率 x1、x5、x10 スライドSW切替) |

||||

| 測定電圧、ロジアナ | CMOS1.5V ~ CMOS3.3V ※スレショルド1.0V固定 最大分析周波数 50MHz ※ロジアナ機能はLMBUF、LHBUFが優れています |

||||

| オシロプローブ | 1MΩ、27pF ※ターゲットGND接続時の重要な注意 ・FETロードスイッチが有り、PCのGNDとターゲットのGNDを未RUN時は分離させます。RUN時はFETを仲介しPCのGNDと同電位になります。異なるGNDは使用できません※ *3 |

||||

| トリガー | 8連続条件シーケンシャル、オシロ+ロジアナ複合条件 | ||||

| 消費電力 | 最大700mA、LDSO1個500mA以下 ※LDSO 2個の場合、別途ACアダプターが必要 |

|

※当ロジックアナライザーは、デルタコア社オリジナル開発です。

記載されている各名称、製品名は、各社の商標、または、登録商標です。 |